#### Integrated circuit;

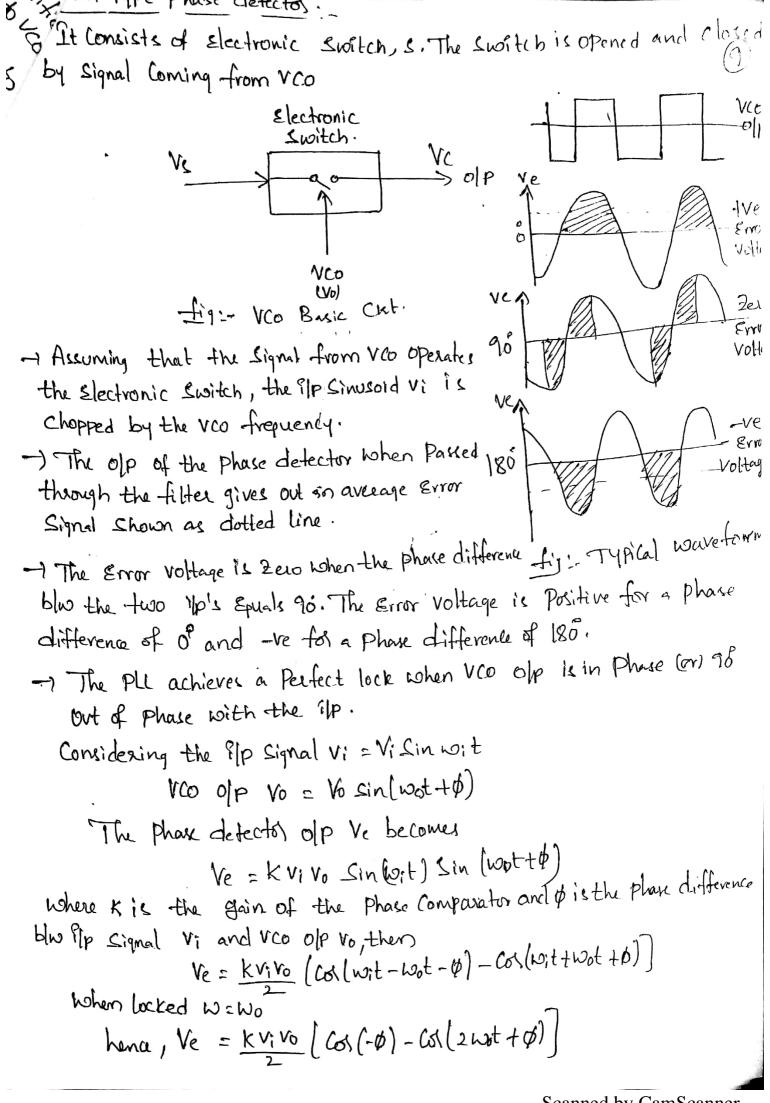

common person uses electronics in \* Now -a-days a limited purposes like radio, TV, Ac, --- all gadgets in real life.

\* But electronics has a great growth in communi--cation industries, control, computer, --- etc.

\* electronics plays major role in industries.

\* electronics is nothing but an integrated circuit.

\* "IC" is a small size and low cost circuit. It consists of both active and passive components are joined together on a single crystal chip of silicon.

-> passive components like resistors, capacitors & inductors. These does not need of external power supply. which absorbs power & stores in the form of energy.

-> active components like transistors & diodes. These one depends on power source. These one modify & control the electrical eignals.

Advantages:

\* small size of Ic and hence increased power density. due to batch processing.

\* Increased system reliability due to elimination of

soldered joints.

\* Improved function performance.

\* Matched devices (input impedance at each port is equal to output impedance).

> Increased operating speeds (Absence of parasitic capacitance)

> reduction in power consumption.

#### Applications :-

- -> Automobiles -> All vehicles like cost, bike, ---

- -> Appliances -> TV, watches, juice makers, --

- -> computers.

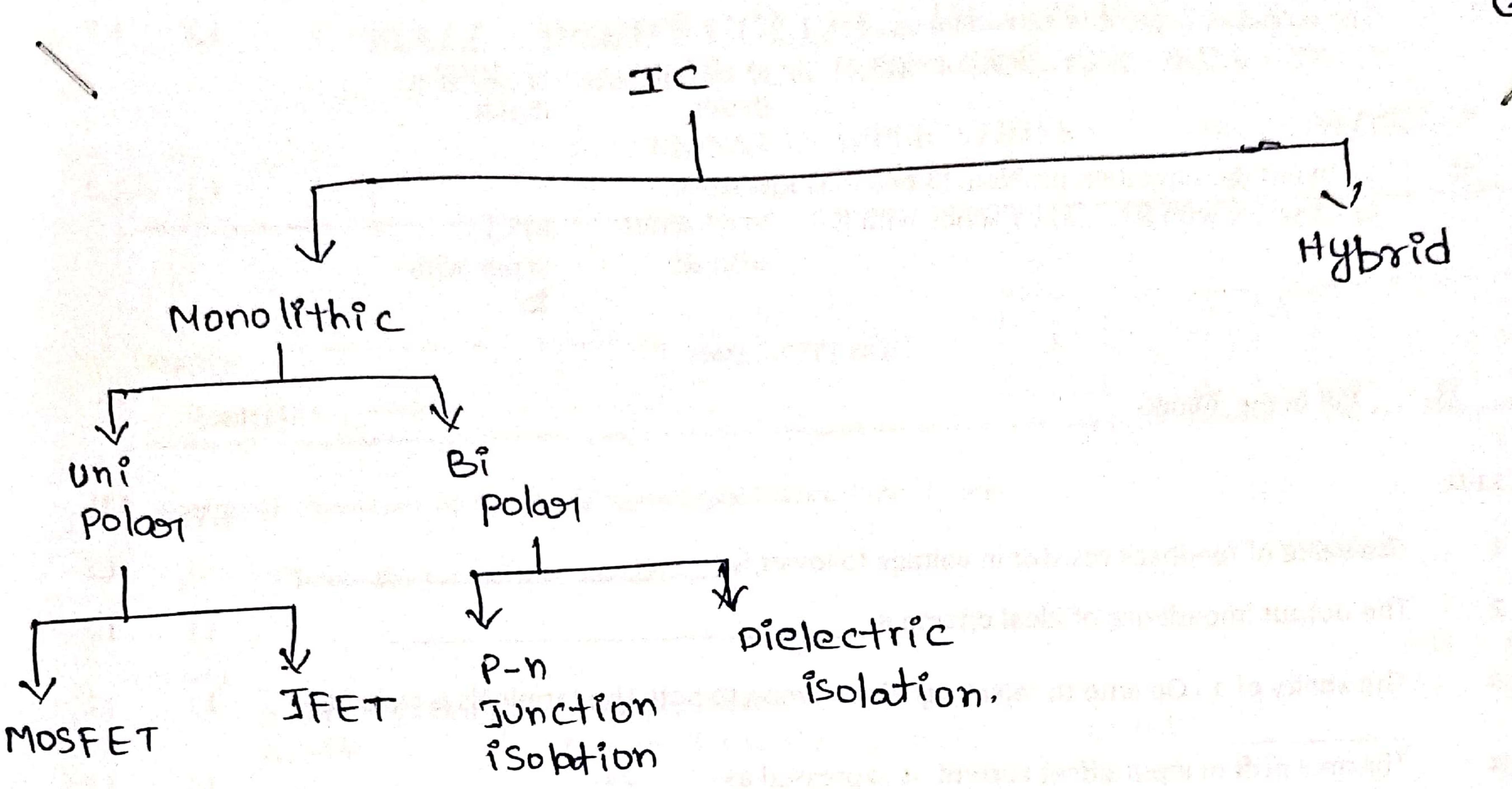

# classification of Icls:

Ic's one chasified into 3 types. They are

- 1. Digital Icls Ex: MP, MC, DSP's etc.

- 2. Analog (or) linean Icls Esci-memorys, sensors, power supply

- 3. Mixed signal Ic's Ex:- Ald&DIA converters, ex

Based on above requirement, there are a different Ic technologies.

- 1- Monolithic technology

- 2 Hybrid technologey

#### Monolethic;-

All circuit components both active and passive elements & their interconnections one manufactured into (or) on top of a single chip of silicon. These one used, where identical circuits one required that why we reduces the cost & more tybrid;

In this, separate components parts are attached to a substrate and interconnetted by using metallization & wire bonds. This is used for custom circuits.

Scanned with OKEN Scanner

active devices used. Ic's one classified as. upon

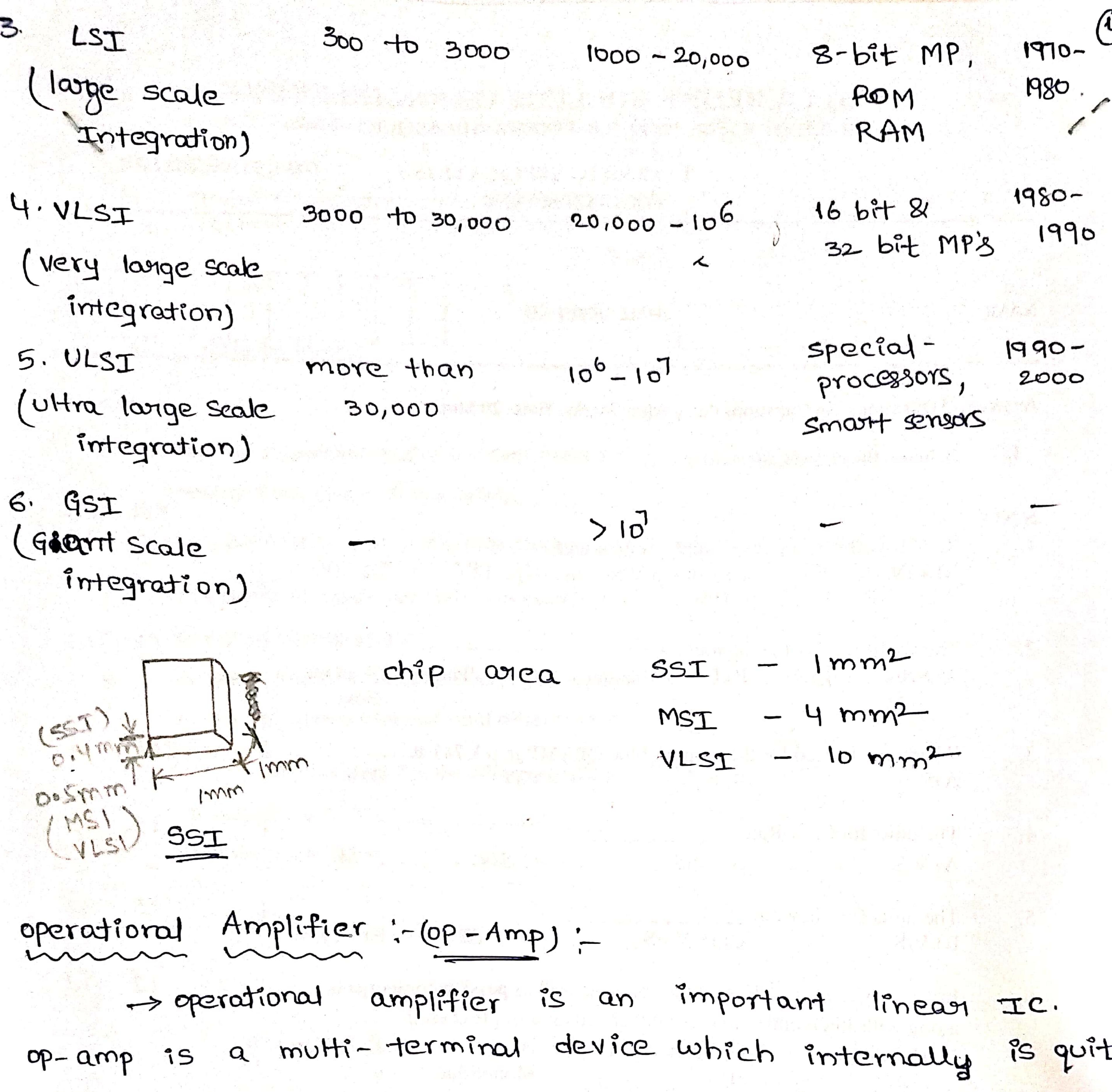

IC chip size and circuit complexity: -> until 1950/8, electronic device technology uses vacuum tube but now-a-days electronics is a result of invention of transistor in 1947. -> the invention of transistor by william B. Schockley walter H. Brottain & John Bondeen of bell telephone laboratory and followed by the development of IC. -> the IC was introduced at the beginning of 1960 by both texas instruments & fair child semiconductors. Invented by

Robert Noyce. -> The size and complexity of Ic's have increased rapidly as shown below.

| Techmology                          | gates/chip | -transistors | Applications             | year      |

|-------------------------------------|------------|--------------|--------------------------|-----------|

| 1. SSI<br>(Small scale              | 3 do 30    | to 0         | logic gates<br>Hip flops | 1960 - 65 |

| Integration                         | 30 Ho 300  | 100-1000     | multiplexers<br>counters | 1965-1970 |

| 2. MSI<br>(medium scale<br>(medium) |            |              | adders                   |           |

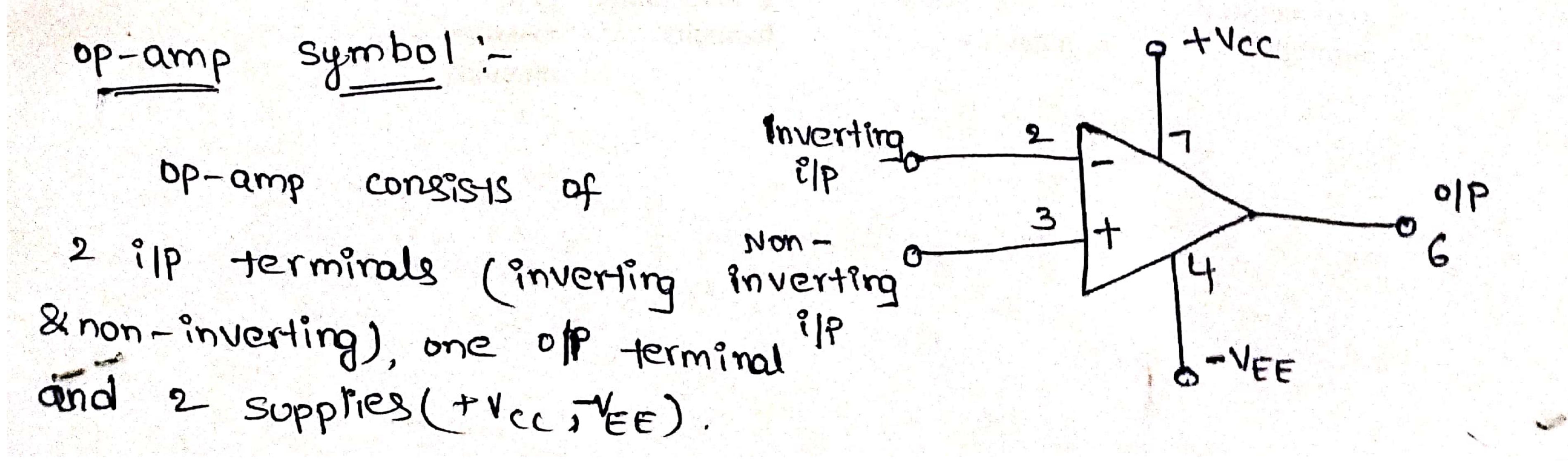

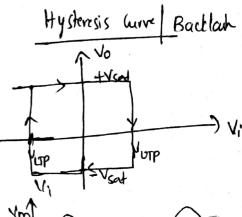

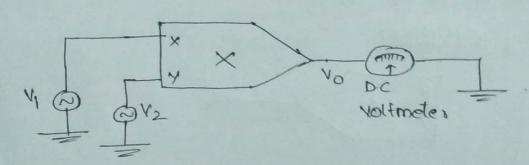

op-amp is a mutti-terminal device which internally is quite complex.

-> op-amp is a direct coupled high gain amplifier usually consisting of one (or) more differential amplifiers and followed by level translator and an olp stage.

op-amp is an Ic that can amplify weak electric signals the basic role of op-amp is to amplify and olp the voltage difference between two 1/p ping.

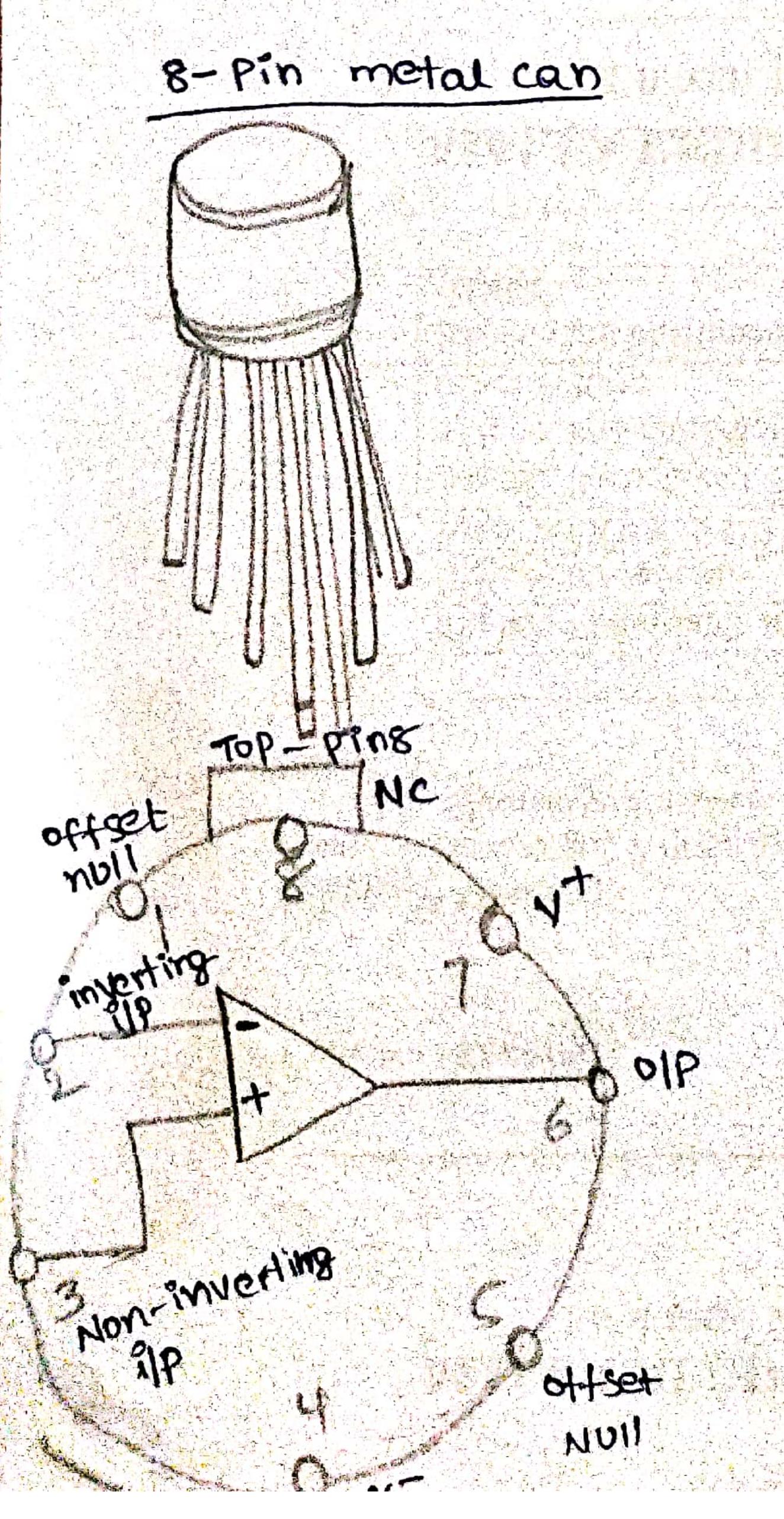

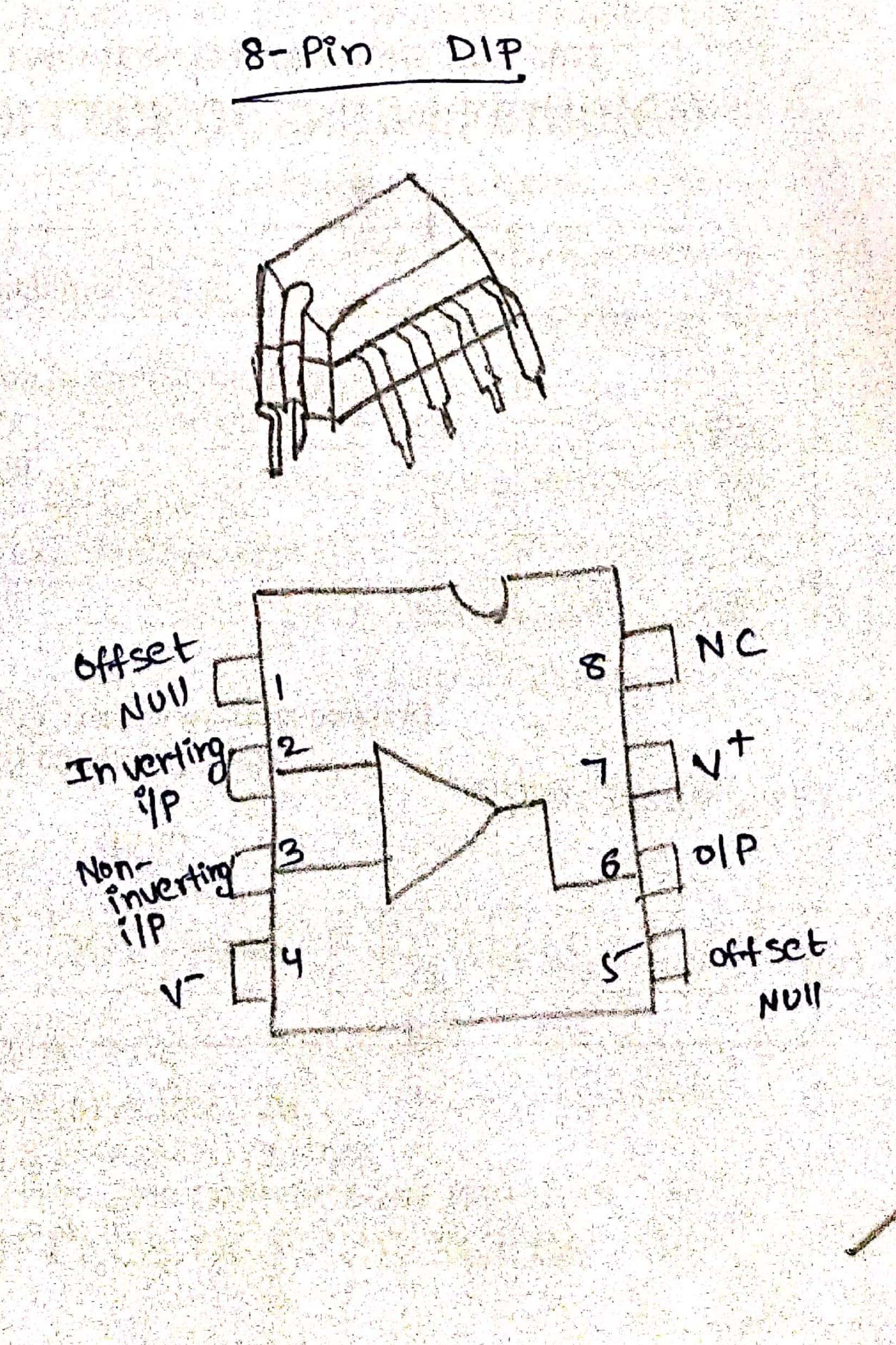

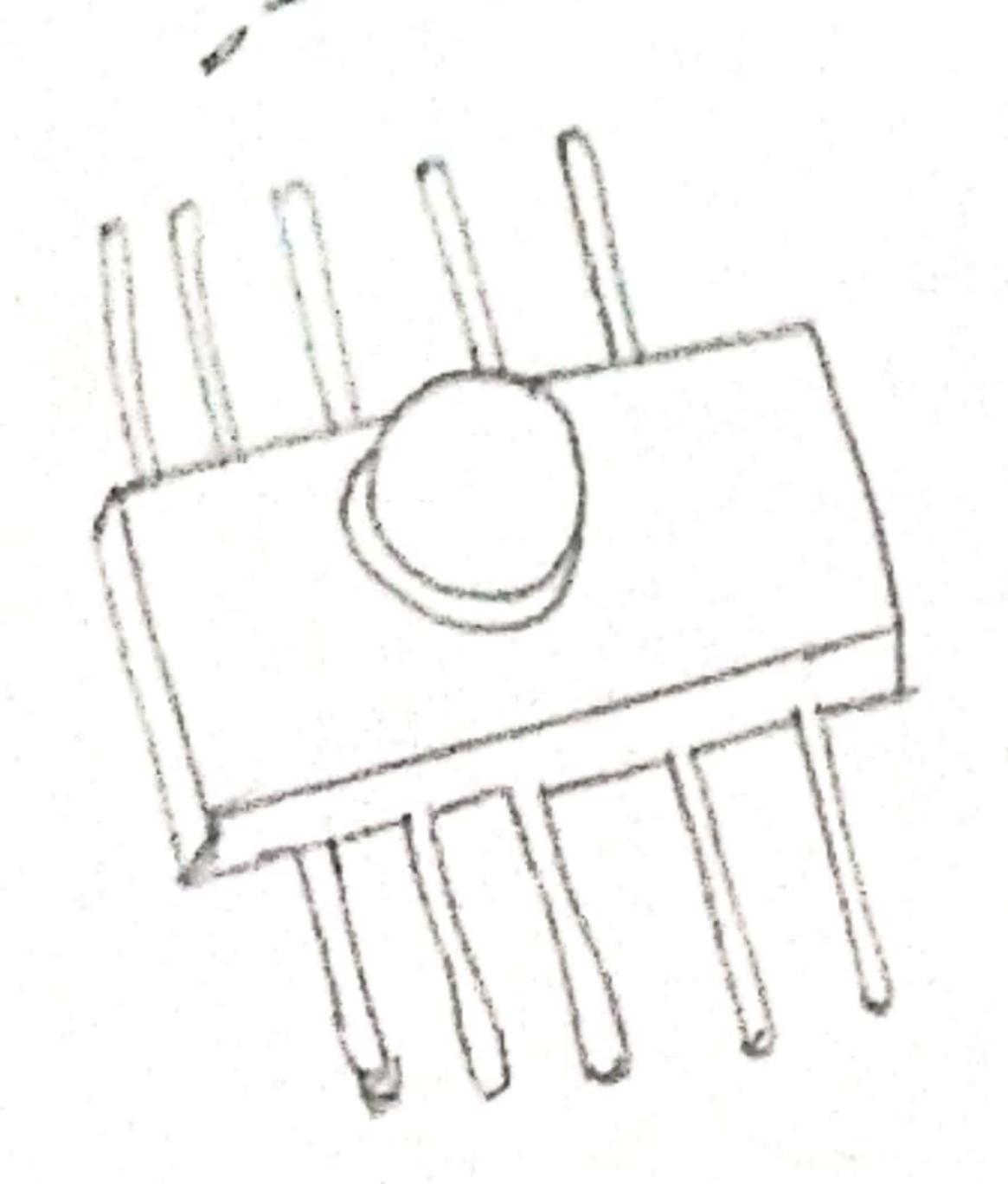

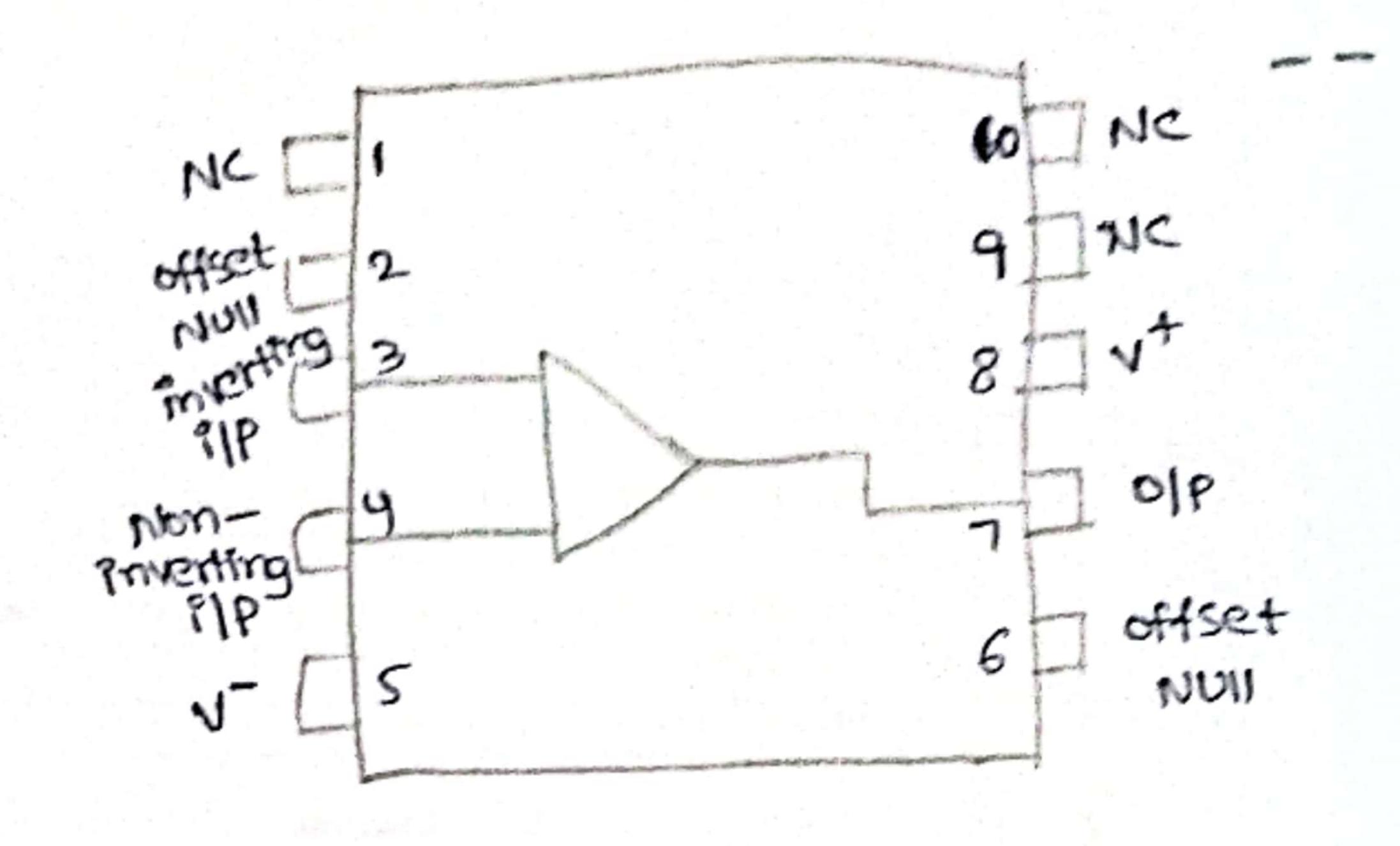

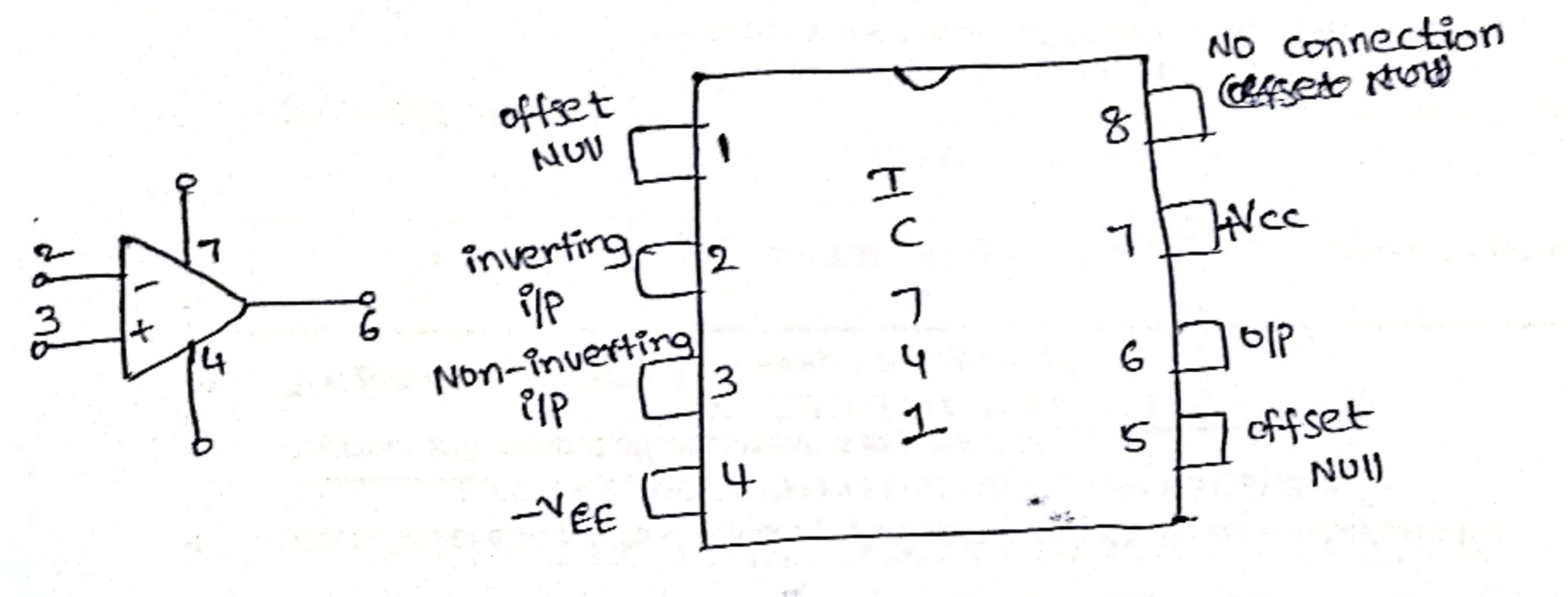

## op-amp packages:-

There we mainly three popular fackages are available.

- 1. Metal can (to)

- 2. Oval in-line (DIP)

- 3. flat package.

The widely used very popular type is MATHI. It is a single op-amp & available in 8-pin can, 8-pin DIP.

Scanned with OKEN Scanner

# Internal diagram of IC741

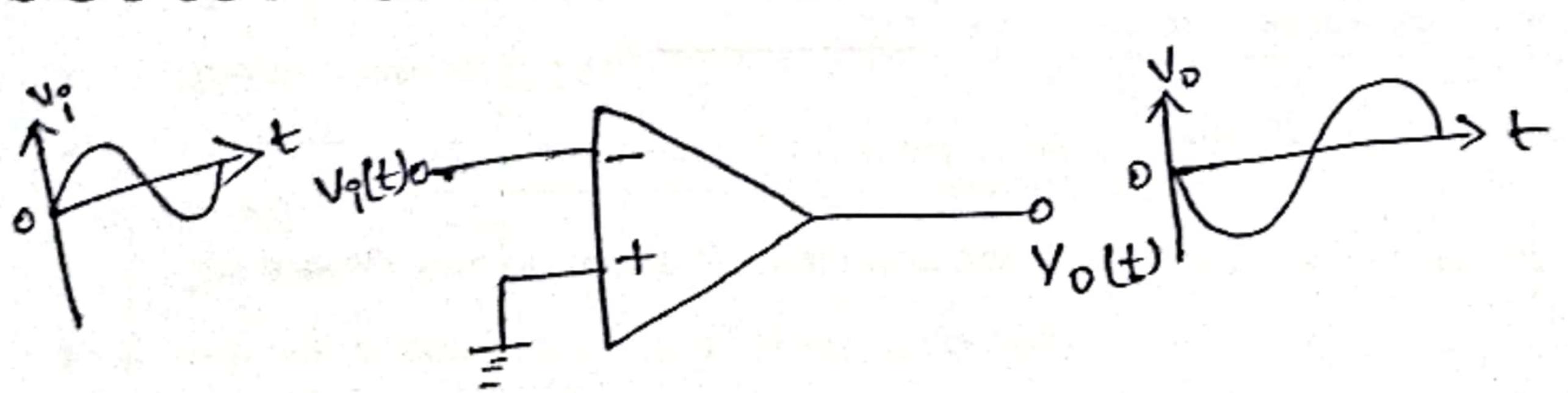

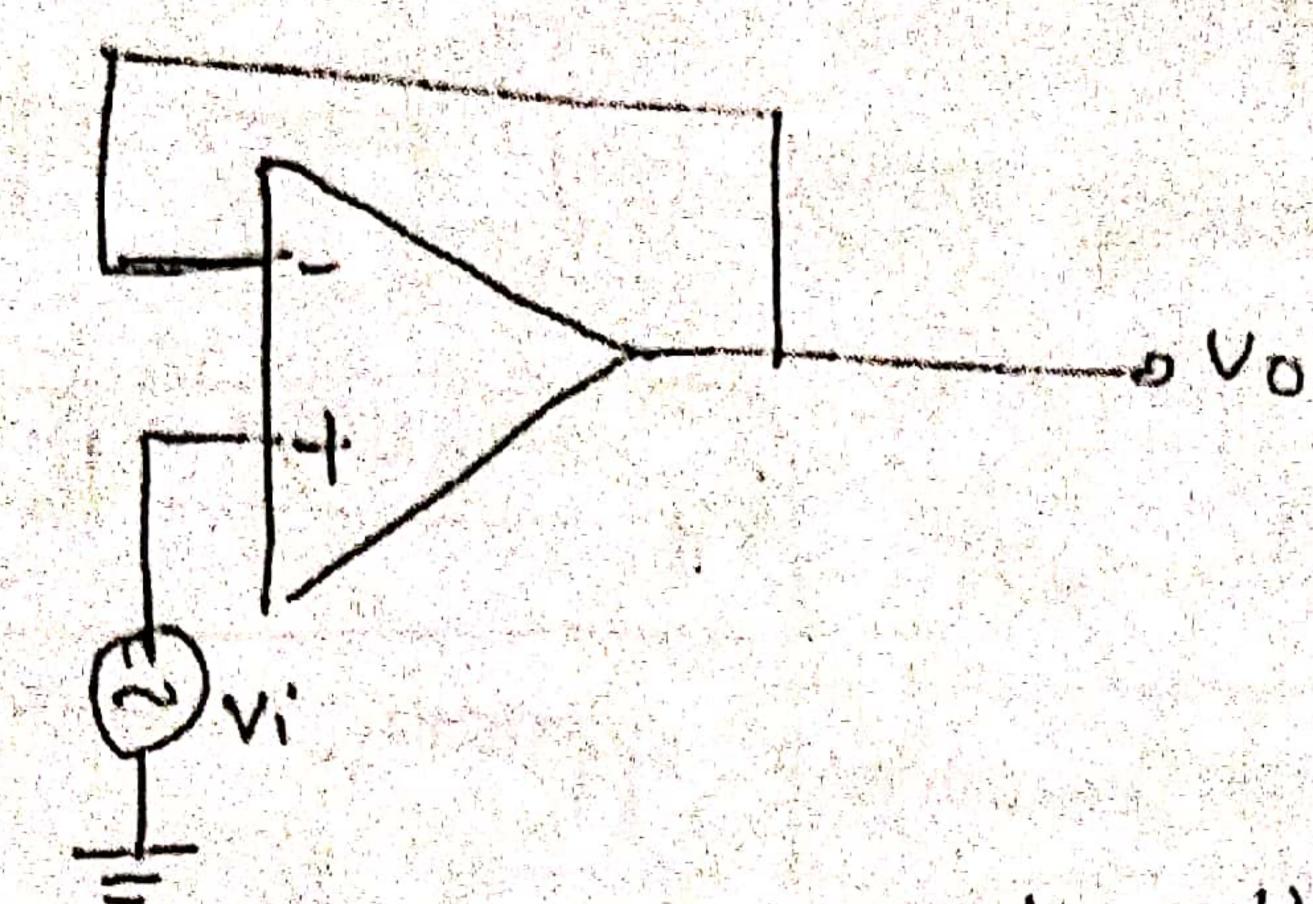

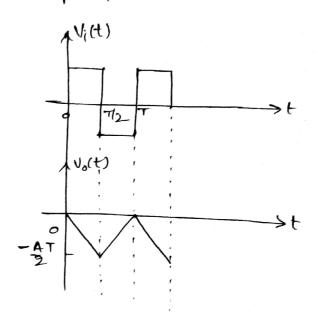

Inverting ill terminal:

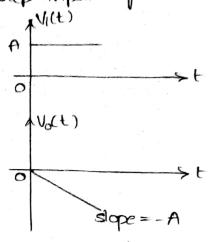

To the above diagram we are applying ilp to the -ve terminal of op-amp & tve terminal is kept grounded.

-> By observing the Vi(t), Vo(t) signals, it is clear that both one out of phase by 180° for that reason the -ve terminal is called inverting ilp terminal.

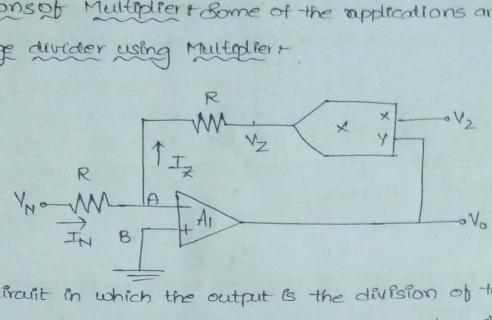

of Mulls over

In the above diagram we apply 1/p signal is grounded.

→ By observing vilt) & vo(t) signals, it is clean that both one in phase so the terminal is called non-inverting ilp terminal.

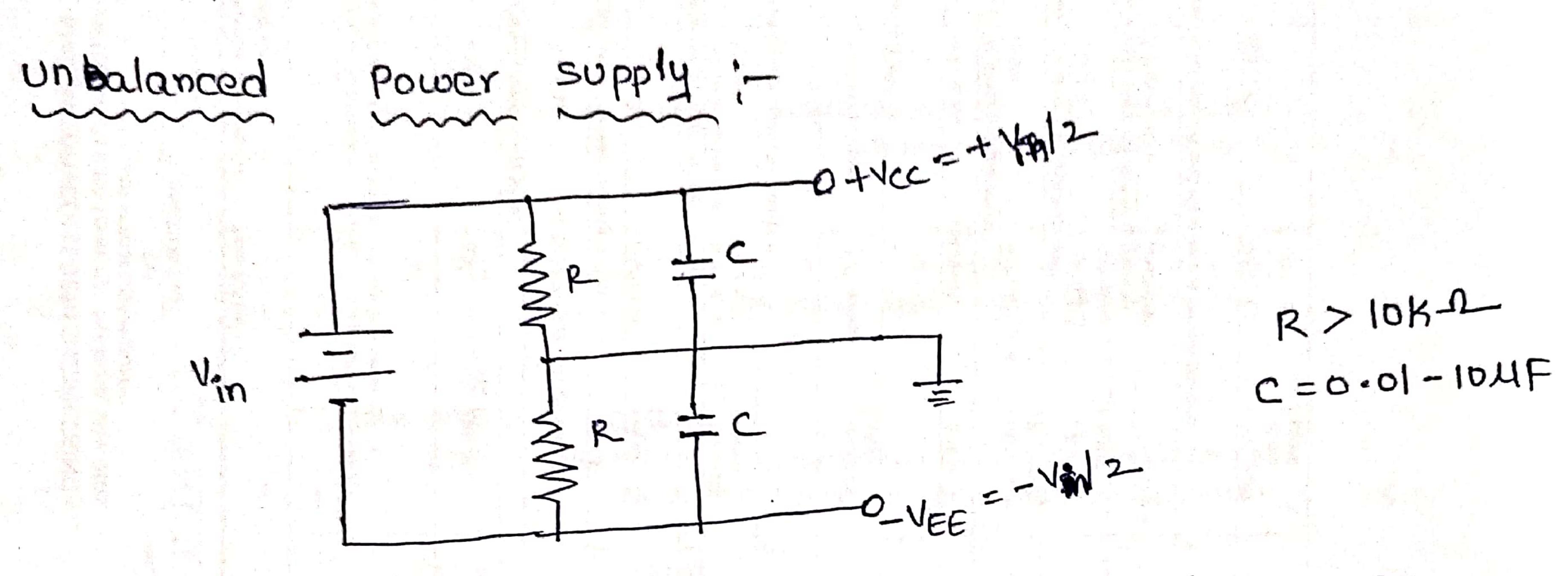

## Power supply:

there are mainly 2 power supply connections in op-amp.

- 1. Balanced Power supply

- 2. Unbalanced power supply

The balanced power supply the two supply voltage magnitude must be equal and the common terminal is kept grounded.

In balanced P. Supply, twice the supply voltage will get applied & it may damage the op-amp. Instead of using two power supplies, one can use a single p.s to obtain N+ & V.

-> the two capacitors provide decoupling of the power supply.

R Vin

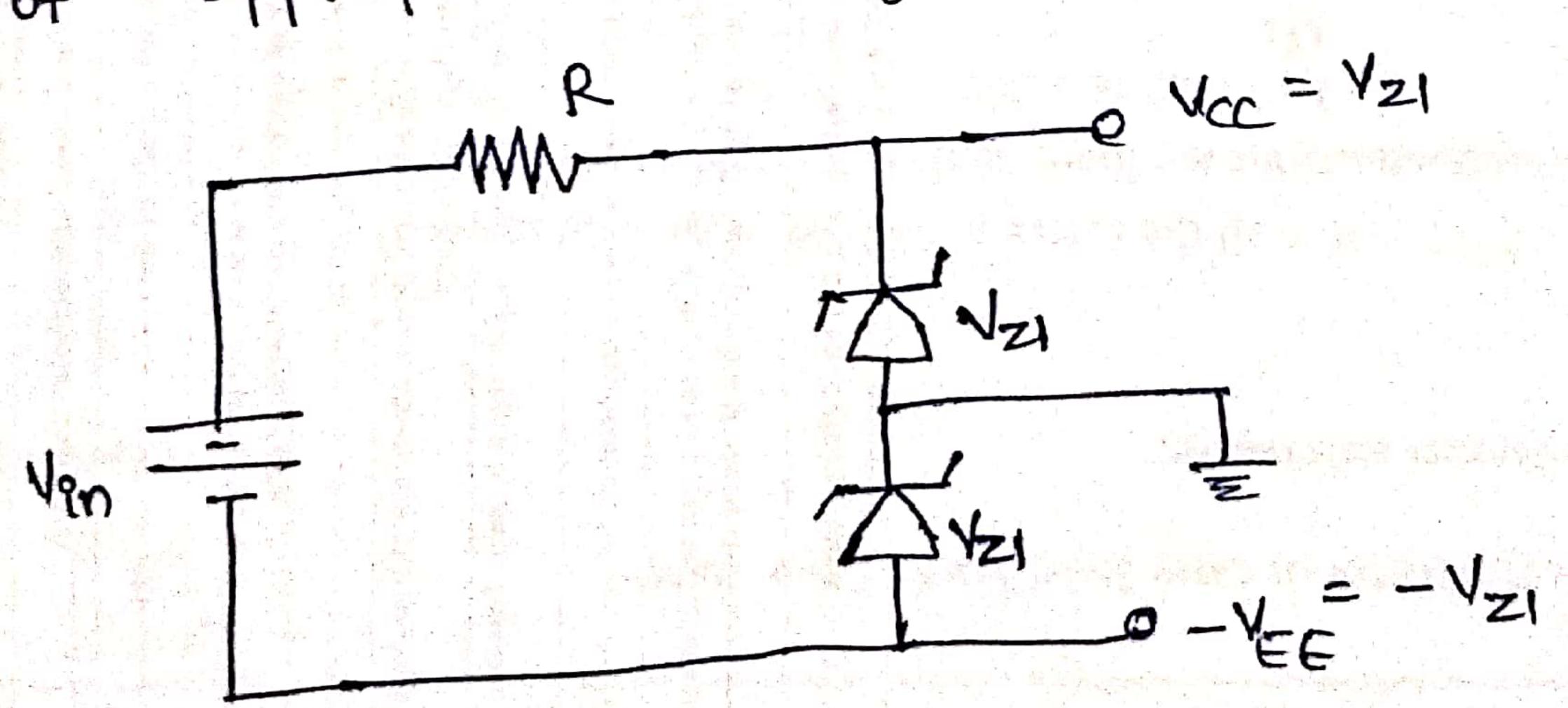

$\rightarrow$  If the voltages required are other than  $\frac{Vin}{2}$  then above circuit is non preferable then we can use zener dides of appropriate voltage rating can be used.

Thany times practically due to mismatch in the devices equal tre & -re voltages one not available, to adjust them a potentiometer can be used as shown below.

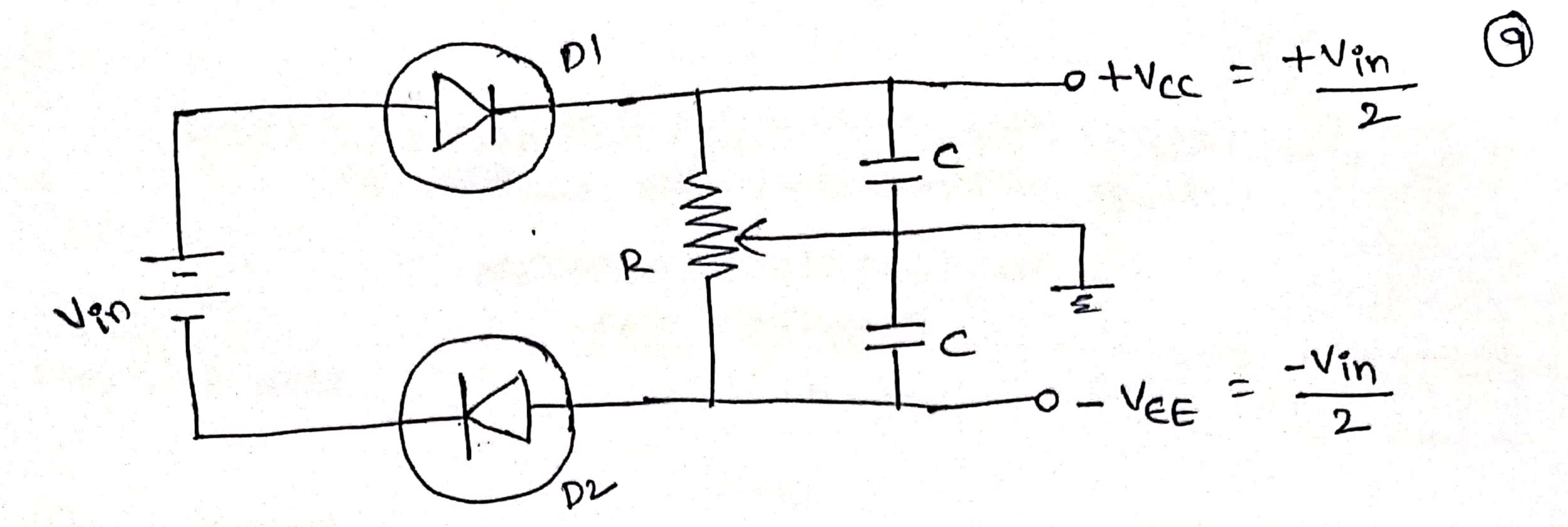

$\rightarrow$  to avoid the damages due to reversal polarities connected to integrated circuit, the diades D1 & D2 can be used.

Features of 741 op-Amp:

- -> Short circuit & overload protection provided

-> large common mode rejection ratio (cMRR) and

- differential nottage ranges. Ideally CMMR is infinity.

- No external freq. compensation is required. It also does not need any external compensation for phase component. This simplifies the circuit design and minimize the number of components used.

- -> offset voltage null capability

- -> No lottch-up problem

- tow power consumption.

## op-amp internal circuit?

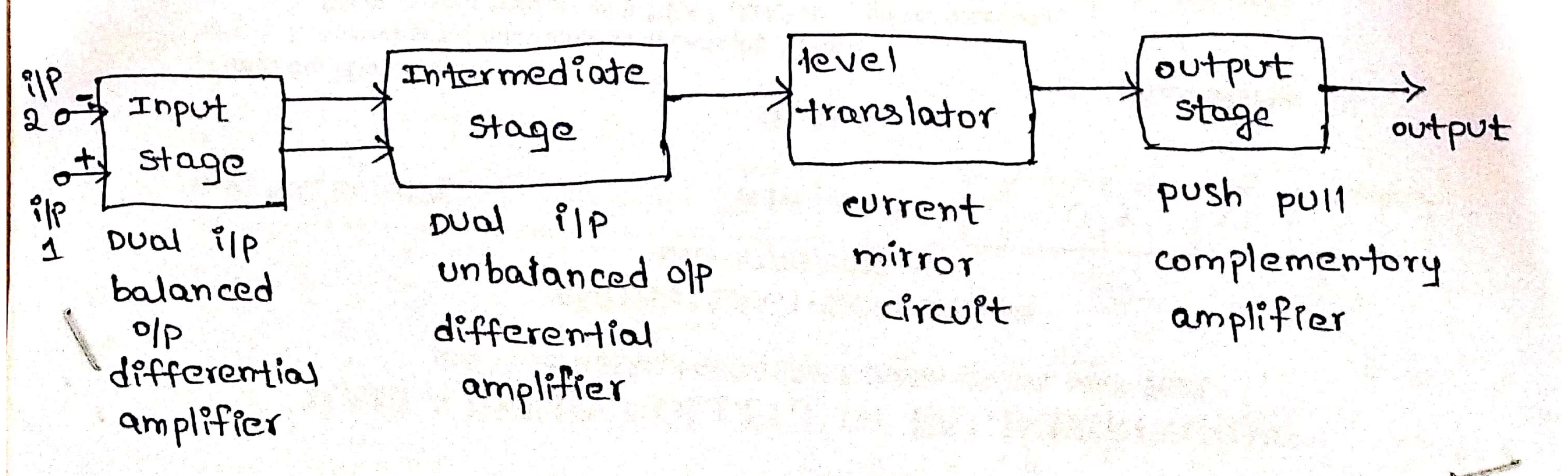

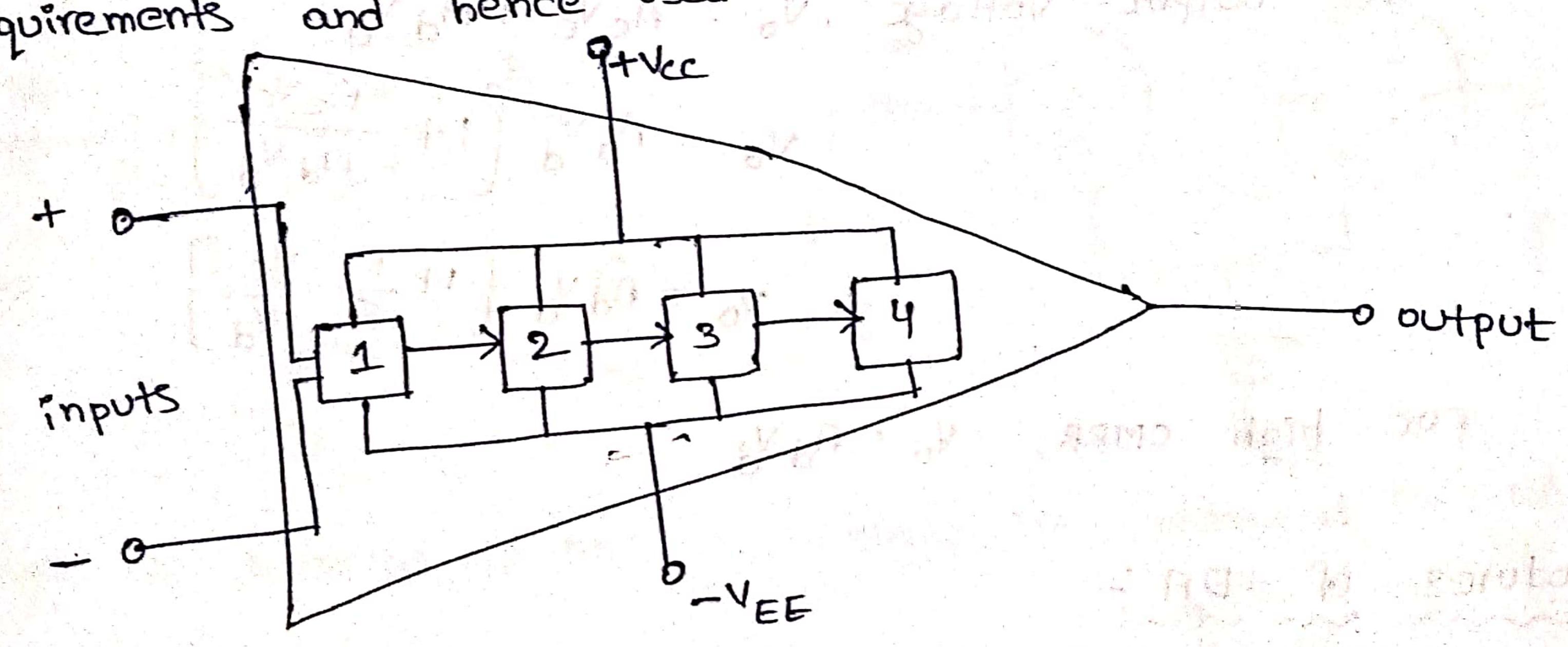

op-amps one available in an integrated circuit form. commertial integrated circuit op-amps usually consists of four cascaded blocks.

scanned with OKEN Scanr

-> All such requirements are achieved by using differential amplifier as the OIP balanced stage

-> the function of differential amplifier is to amplify the difference between the two ilp signals. -> This stage provides most of the voltage gain of THE LY STATE OF THE STATE OF TH the amplifier.

## Intermediate stage:

-> the old of the ilp stage drives the next stage which is an intermediate stage

-> This is another differential amplifier with dual ilb unpalanced (single ended) output.

-> The overall gain requirement of the op-amp is very high.

### level shifting stage:-

- -> All the stages one directly coupled to each other. As the op-amp amplifiers, d.c signals are also directly coupled.

- -> Because of that the DC level is raises stage by Stage such a high dic voltage level may drive the transistors into saturation.

- this may cause distortion in the output

- -> Hence before—the OIP Stage, it is necessary to bring such a high de voltage level to zero volts wirit ground.

→ the level shifter stage brings the d.c level down to ground potential, when no signal is applied at the ilp terminals.

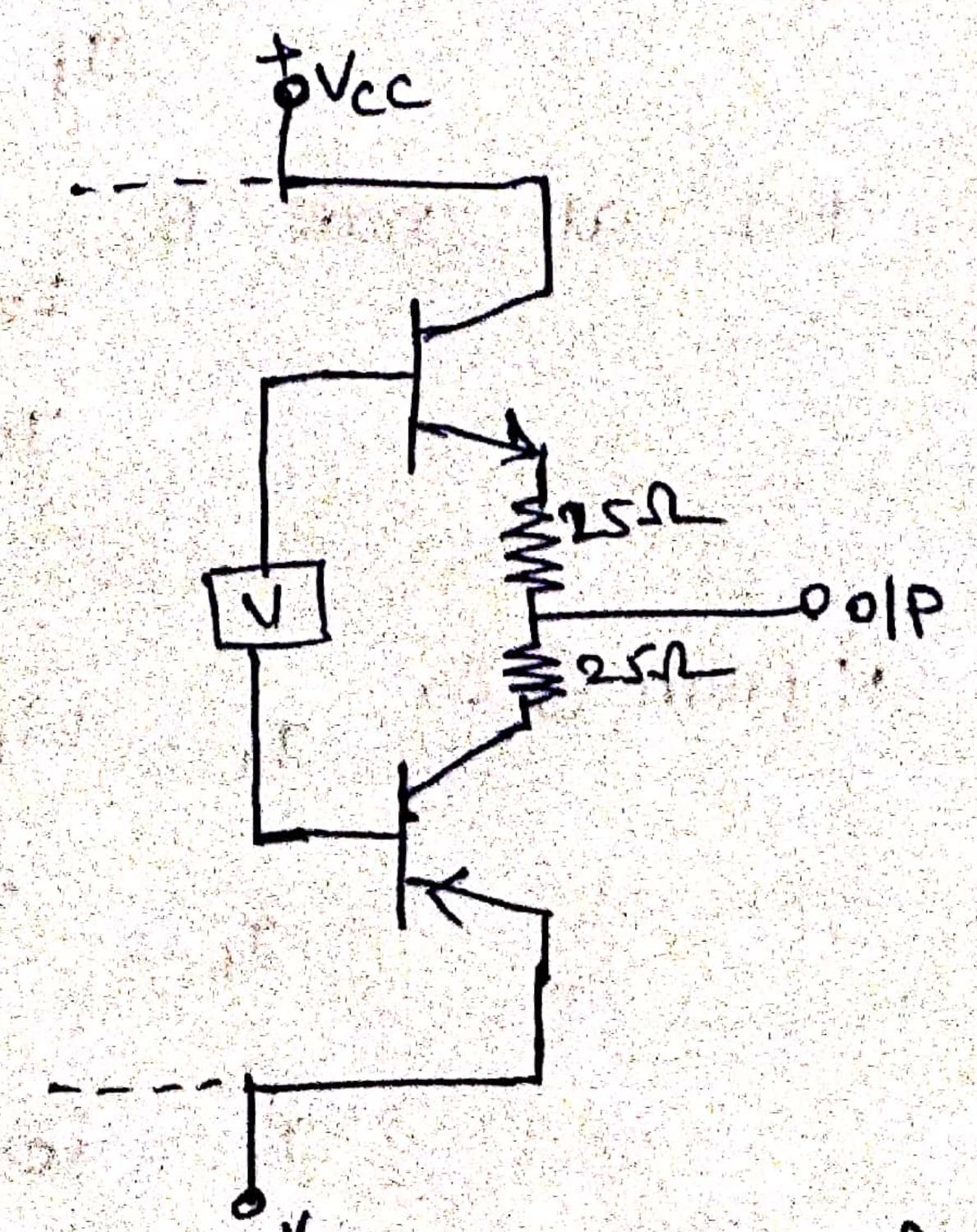

### output stage:

- > The basic requirements of an output stage one \* low output impedance

- \* longe AC

- \* output voltage swing

- \* high current sourcing & sinking capability

-> the push pull complementary amplifier meets all these requirements and hence used as an olp stage.

#### Differential Amplifier:

- -> It is the basic building block of op-amp.

- -> It amplifies the difference between two input voltage signals and rejects the common-mode signals, Hence it is called as differential amplifier.

# common-mode Rejection Ratio (CMRR):-

the ability of a differential amplifier to reject a common mode signal is expressed by a ratio called common-mode rejection ratio.

Scanned with OKEN Scanne

defined as the ratio of the differential Voltage gain, Ad to common mode voltage gain, Ac.

-> For ideal DA, Ac=0 then CMRR is infinite.

-> For practical DA, Ad is large, Ac is small hence CMRR, in dB = 20 log  $\left(\frac{Ad}{Ac}\right)^{\frac{1}{100}}$

CMRR in dB = 20 log

$$\left| \frac{A_d}{A_c} \right|$$

dB

-> The output voltage, vo = Acvc+Advd

\* High differential voltage gain

# low common mode gain

\* High CMRR

\* High ilp impedance

\* low op impedance

\* lange bandwidth

Amplifiers : Types of Differential 4 types of DA18. There one

1. Dual ilp balanced olp DA

2. Dual ilp unbalanced olp PA

3. single ilp balanced olp DA

4. single ilP Unbalanced olp DA.

To the old is taken between the two collector terminals, it is called balanced old (or) double ended old.

→ If the olp is taken between one collector w.r.t. ground, it is called unbalanced olp (or) single ended olp.

-> If the signal is given to both the ilp terminals, it is called as dual ilp.

The signal is given to only one ilp terminals and other terminal is grounded, is called single ilp (or) single

pual ip balanced olp DA

single ila balanced ola DA.

oval ilb unbalanced old DA

single ilp unbalance olp PA.

Scanned with OKEN Scanne

- 1. Difference voltage, 11d = 1,-12

- 2. Differential output voltage, Vo = Ad Vd

- 3. Differential gain,  $A_d = \frac{V_0}{V_d}$  (or)  $A_d = \frac{V_1 V_2}{2}$  (or) 20  $\log \left( \frac{V_0}{V_d} \right)$  (inds)

- where A, & A2 one the gains of two signal voltages of v, and v2 respectively.

- 4. common-mode signal voltage,  $V_c = \frac{V_1 + V_2}{2}$

- 5. common-mode gain, Ac =  $\frac{V_0}{V_c}$  (or) Ac = A1 + A2 (or) 20 log  $\frac{V_0}{V_c}$  (in dB)

- 6. output voltage due to common mode signal is vo=veAc

Scanned with OKEN Scanne

7. Total output voltage for any differential amplifier is  $v_0 = A_d v_d + A_c v_c$ .

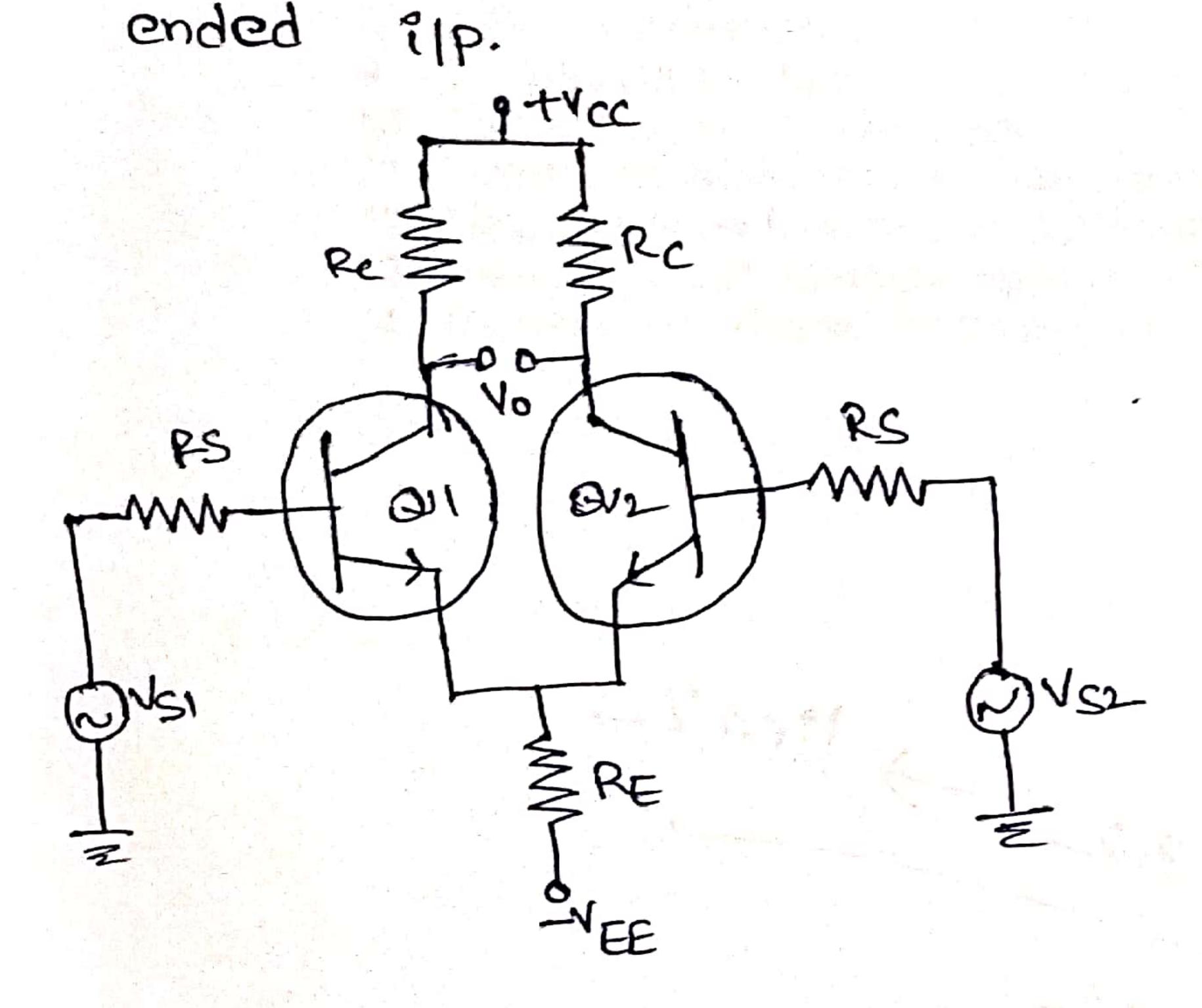

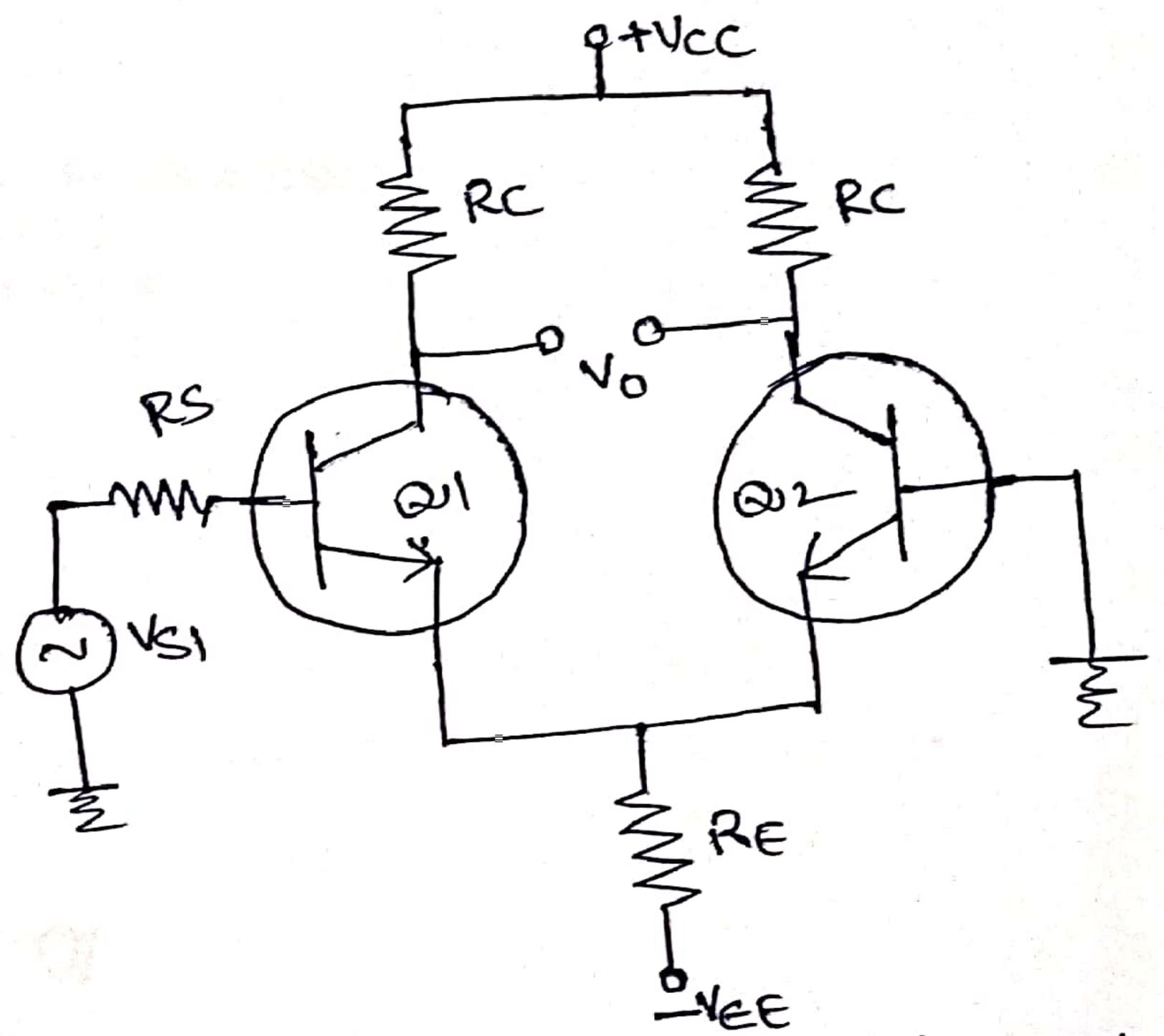

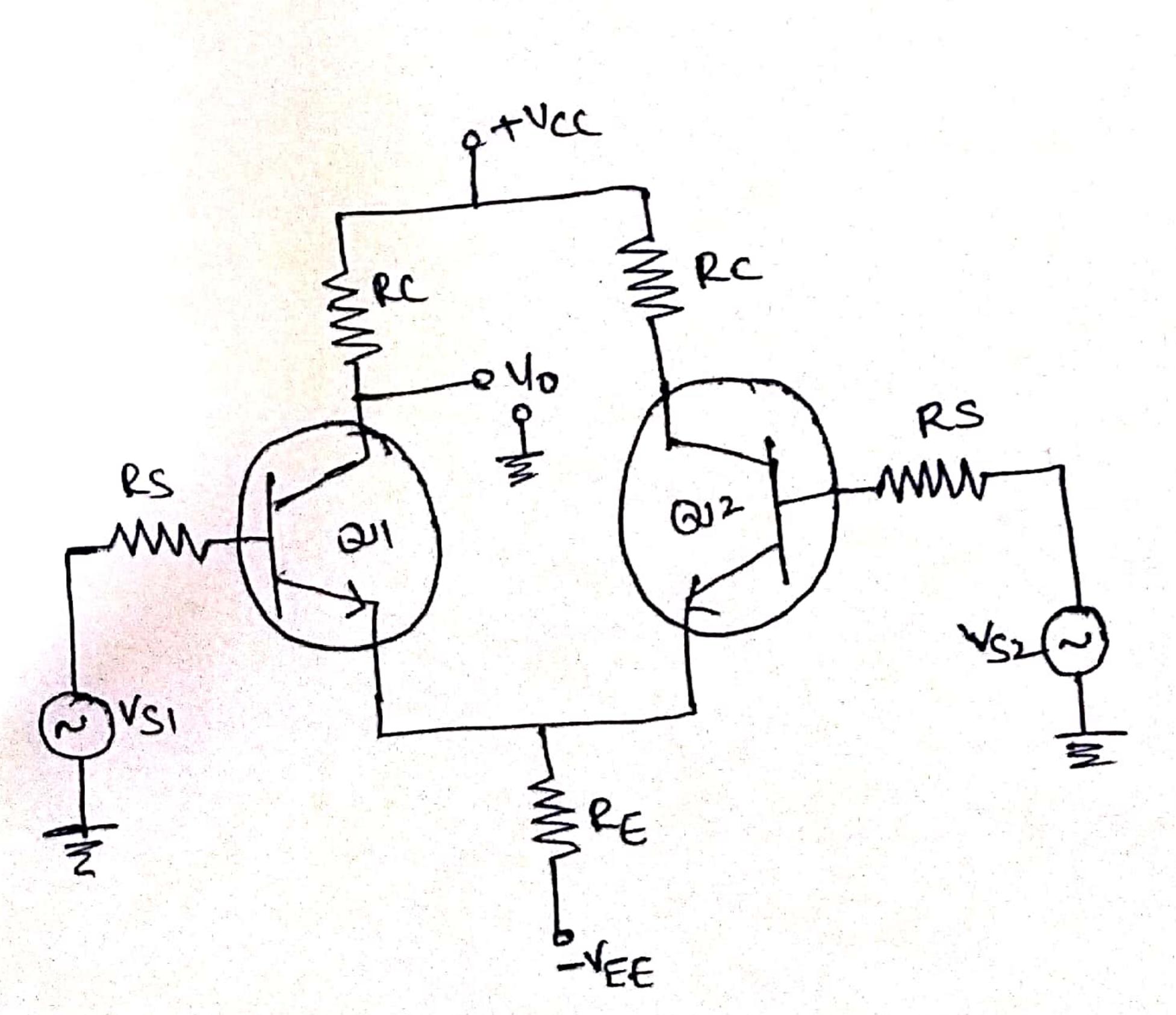

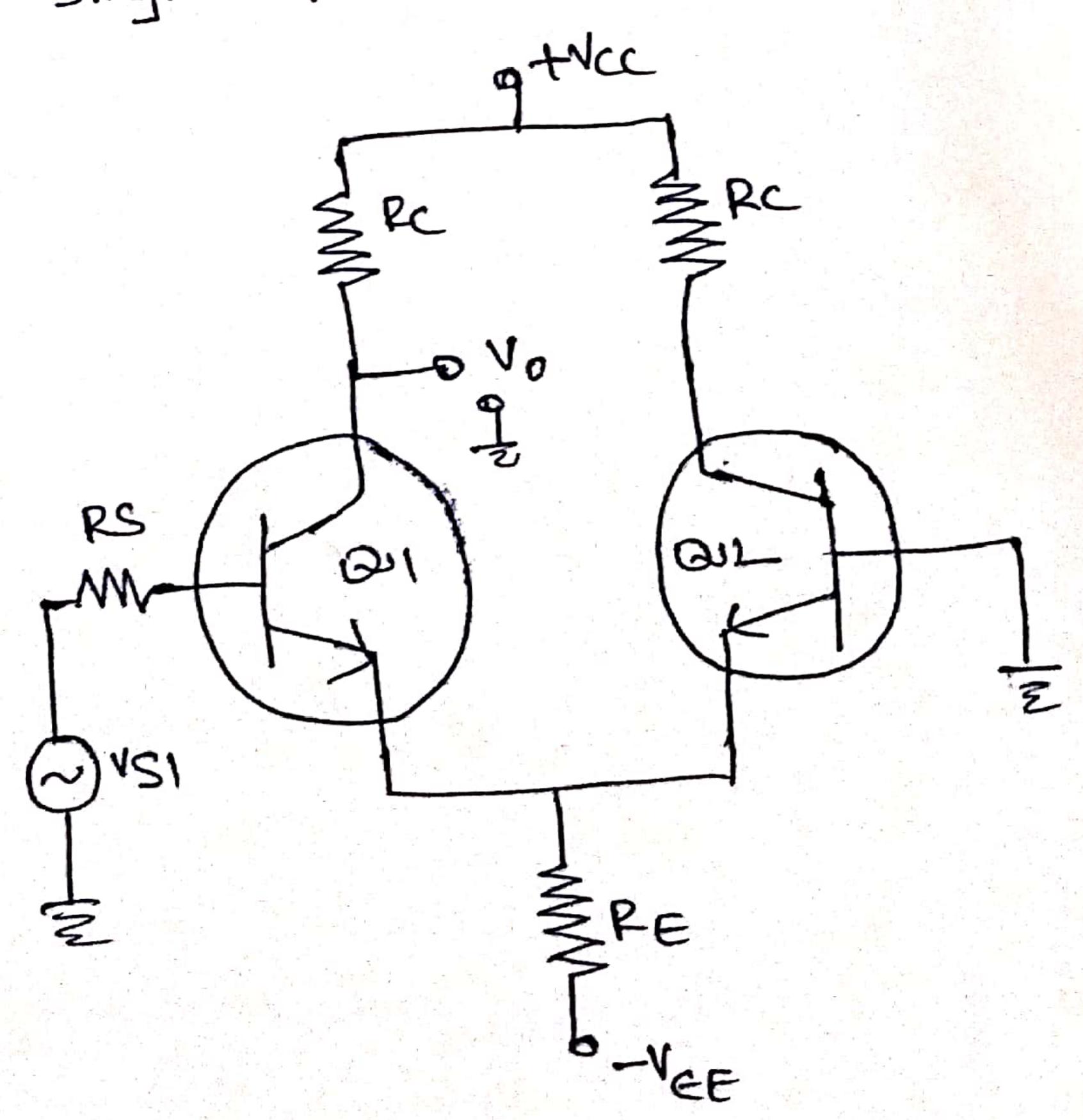

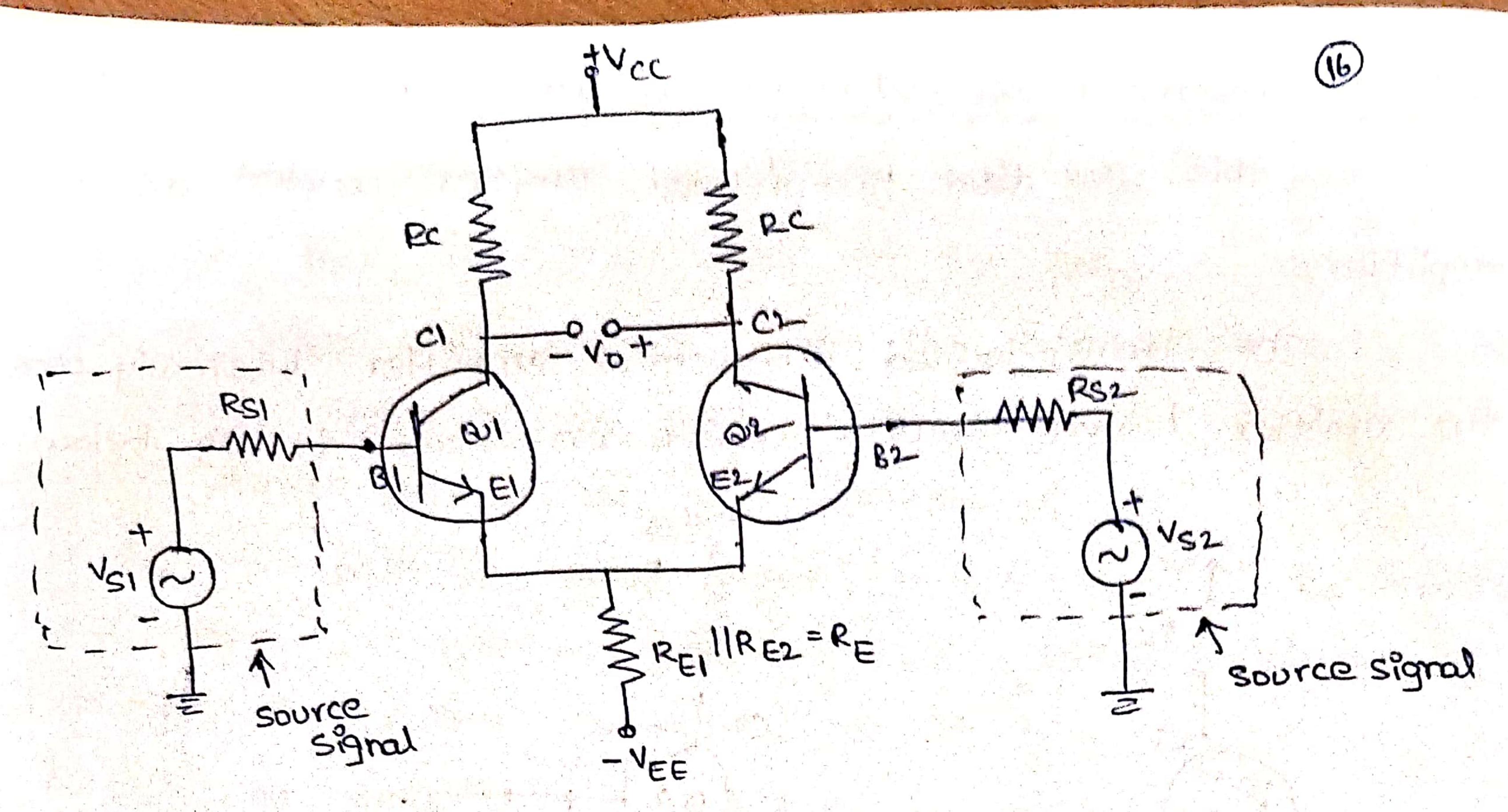

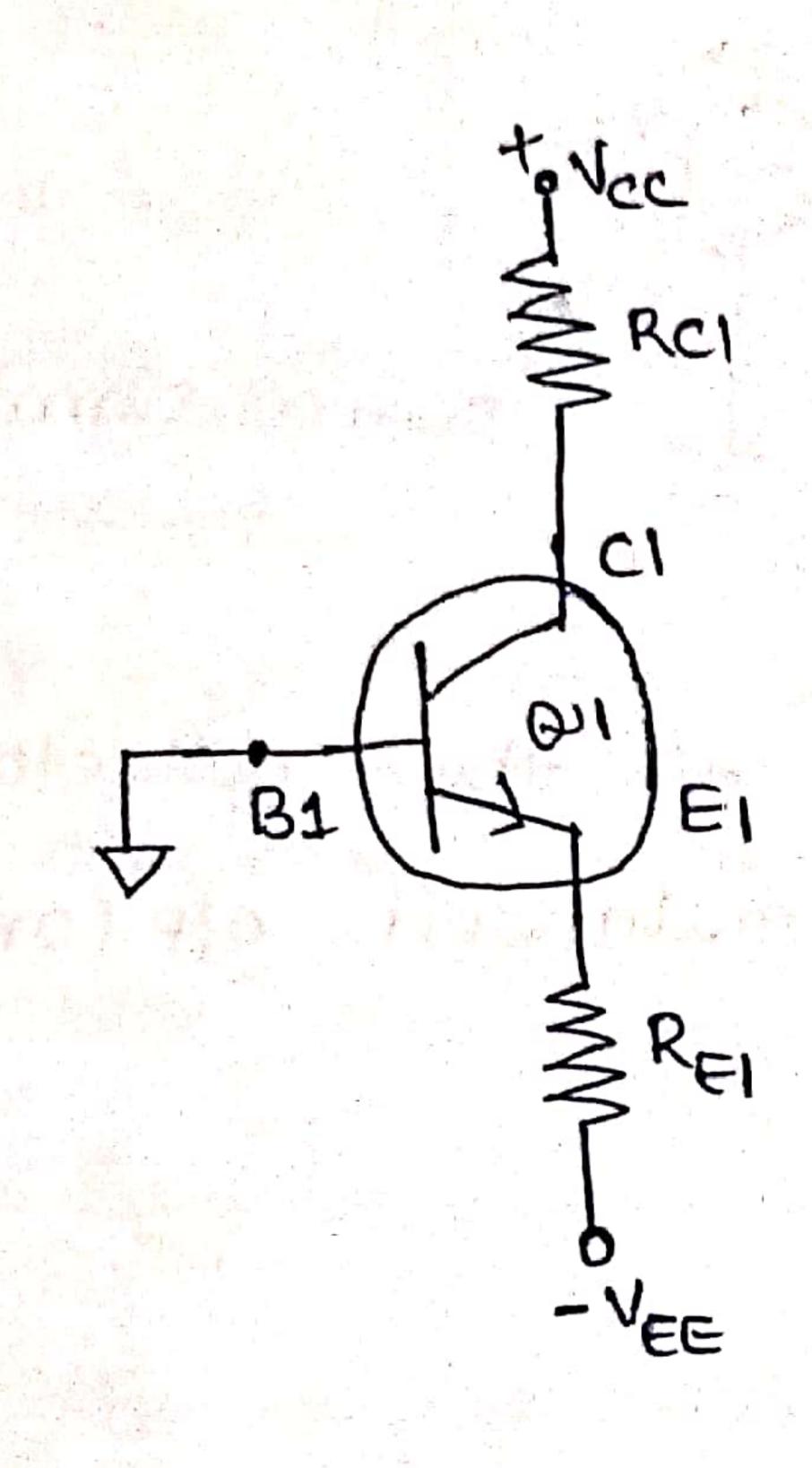

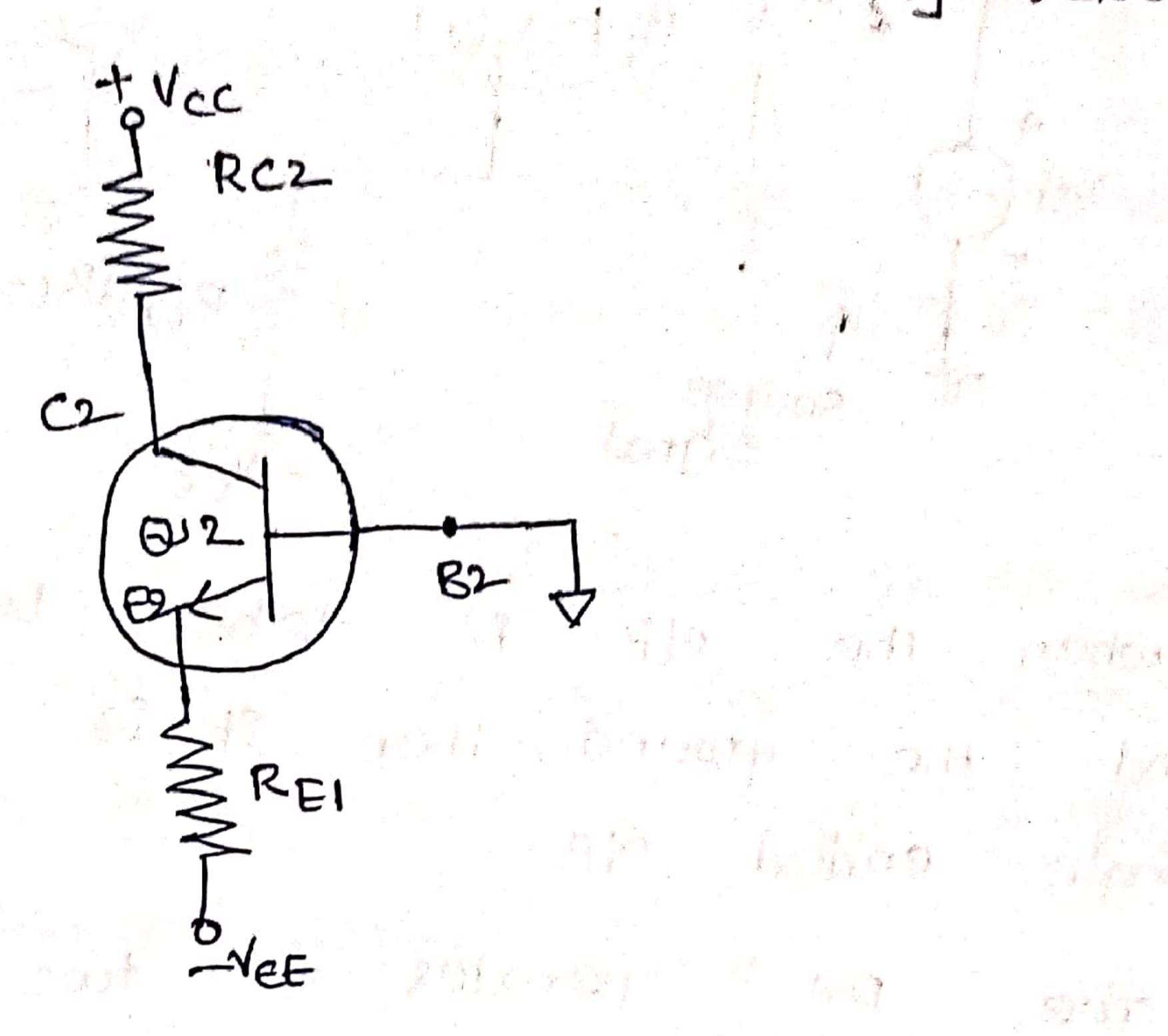

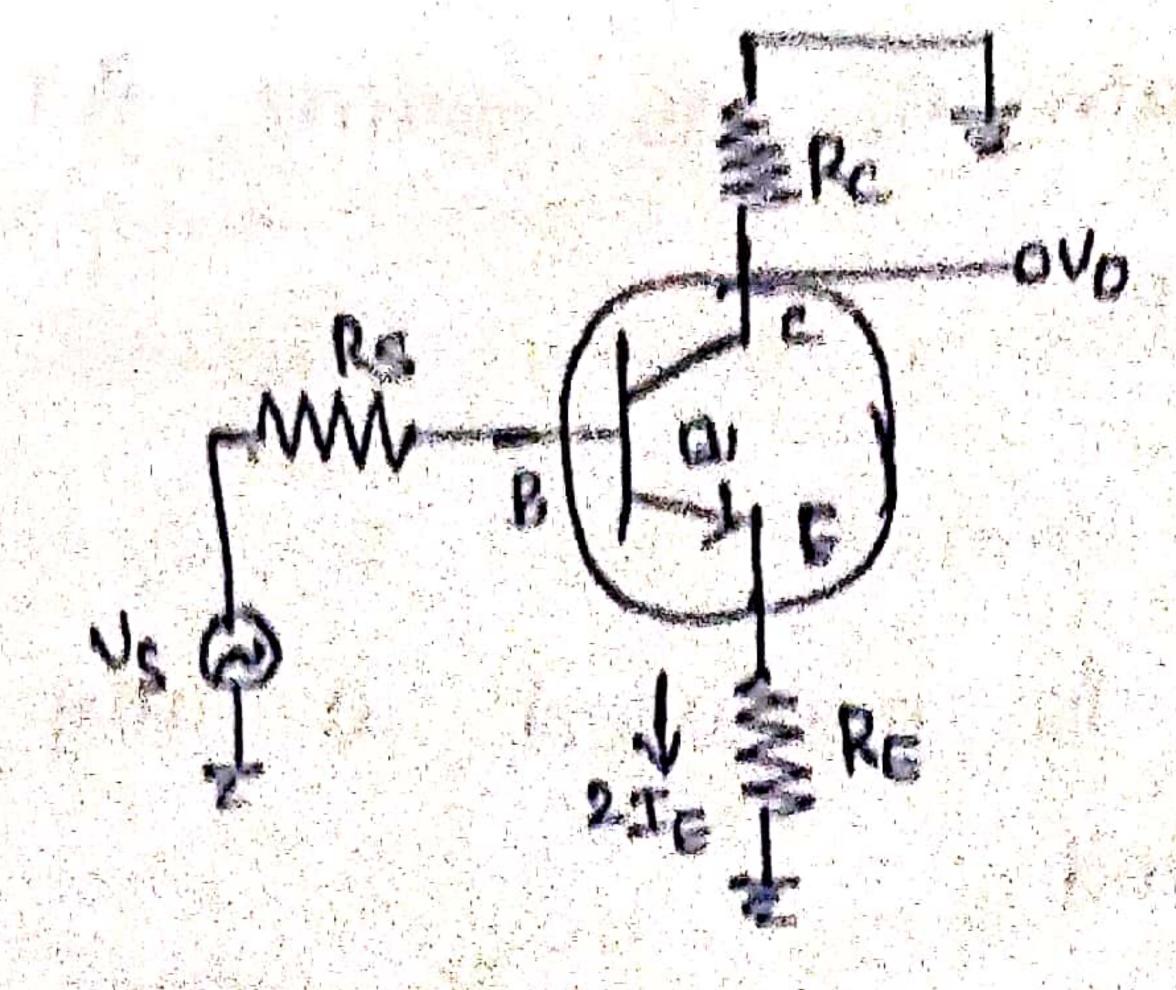

balanced of differential amplifier; emitter coupled differential This is also Known as amplifier.

The transistorised differential amplifier basically uses the emitter biased circuits which are shown in fig. below.

on & one having exactly matched -> the two transistors The transfer of the state of th characteristics.

collector and emitter resistances Rc1, Rc2, Re1 -> The two equal. and REZ ane

REI = RE2 and RCI = RC2 = RC 1 Vcc1 = 1- VEE1

i. the magnitudes must be equal

-> the dual ilp : Halanced olp DA can be obtained by coupling both emitters of the emitter brased circuits and is Shown below fig.

-> If the collector olp is taken between two collector terminals without any ground, then it is called as old (or) double ended old (or) floatting pop.

of the collectors taken between any olP. is -> when the the ground, then it is called as unbalanced off (or) and single ended olp.

DA operates in two modes. -> The

- 1. Differential mode operation

- 2. common mode operation.

Differential mode operation:

\* Differential mode means vs1 + Vs2' consider the two ilp signals which are same in magnitude but 180° out of

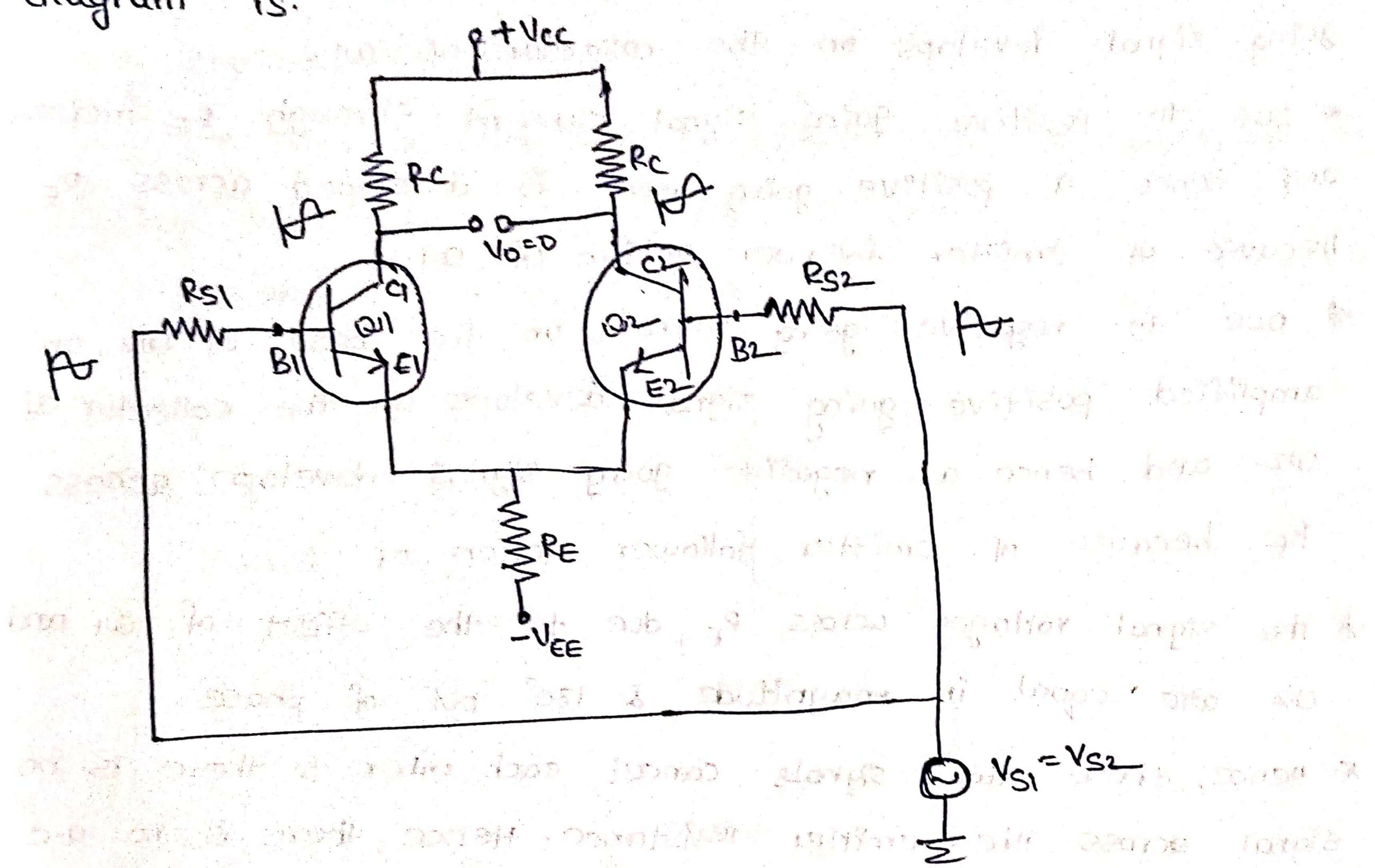

Dual ilp balanced olp differential amplifier:

This is also known as emitter coupled differential amplifier.

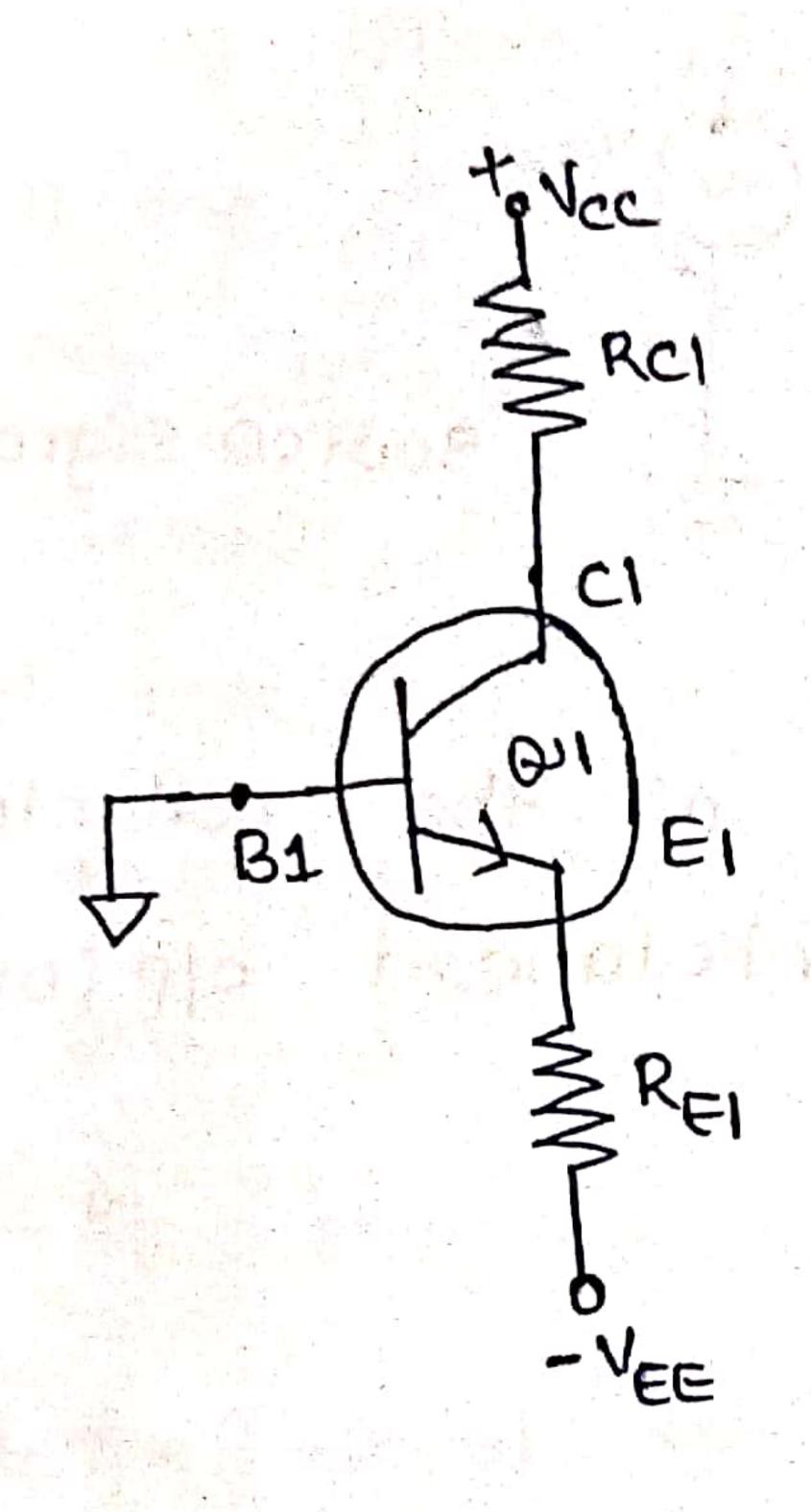

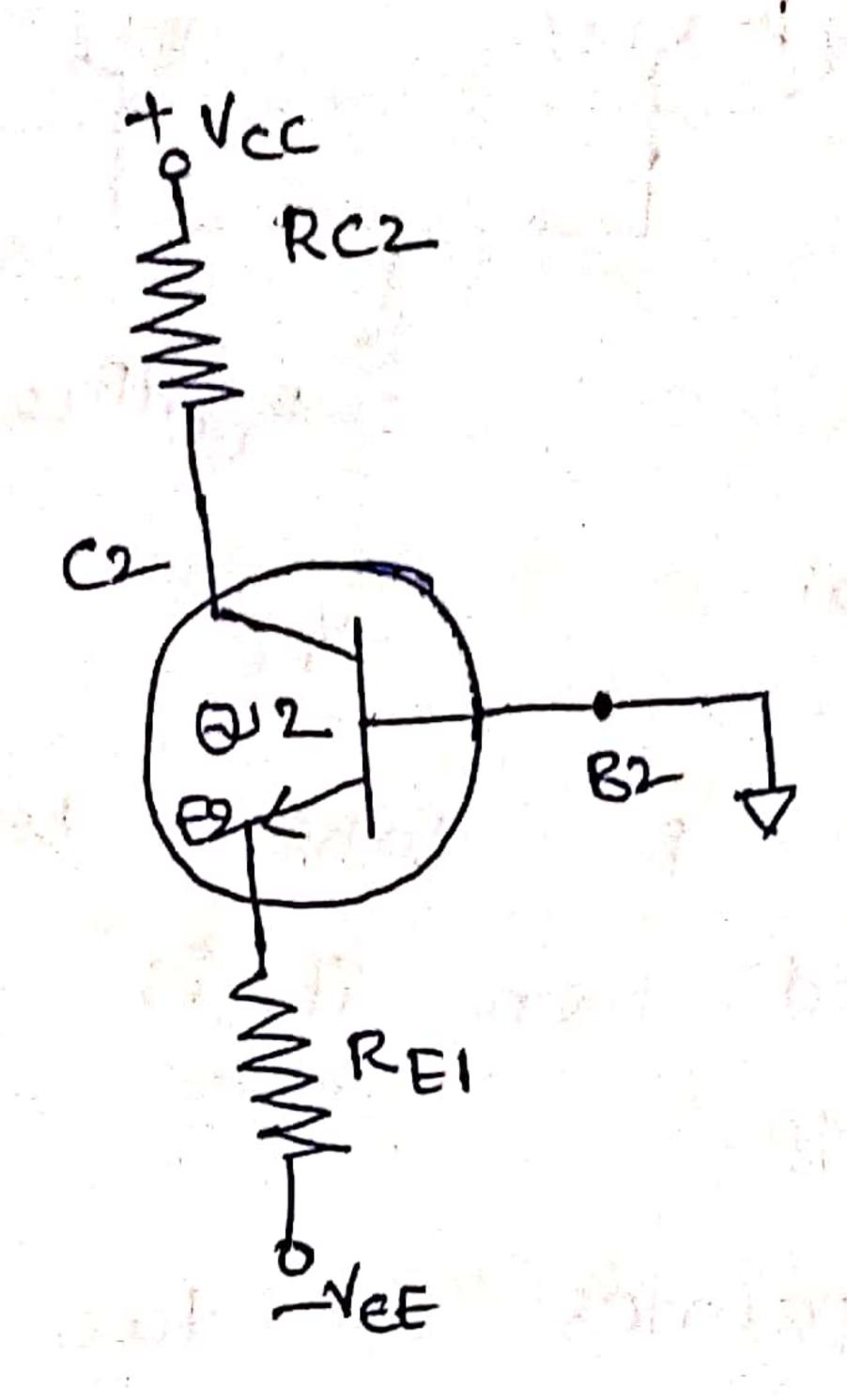

the transistorised differential amplifier basically uses the emitter biased circuits which are shown in fig. below.

and territory with the territory of the

→ the two transistors on & Que having exactly matched characteristics.

The two collector and emitter resistances  $Rc_1, Rc_2, Re_1$  and  $Re_2$  are equal.

$$R_{CI} = R_{C2} = R_C$$

;  $R_{EI} = R_{E2}$  and  $|V_{CC}| = |-V_{EE}|$

... the magnitudes must be equal

The dual ilp Balanced olp DA can be obtained by coupling both emitters of the emitter brased circuits and is shown below fig.

If the collector olp is taken between two collector terminals without any ground, then it is called as balanced olp (or) double ended olp (or) flootting opp.

anned with OKEN Scar

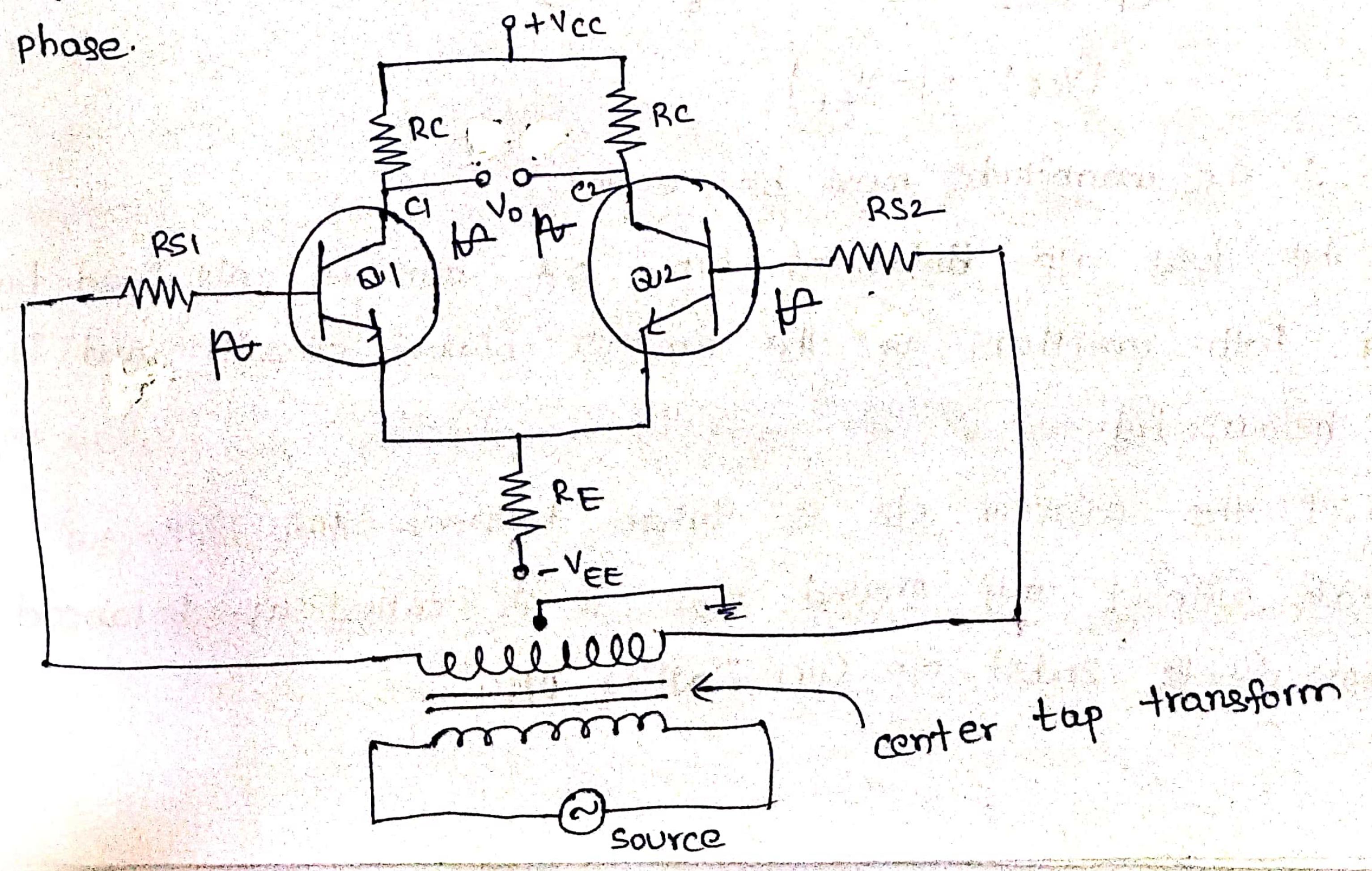

the help of center tapped transformer, we are getting two signals with same magnitude and has 180° phase shift. \* Assume that, the sine wave on the base of al is

positive going while on the base our is negative going with a Positive going on the base of Q1, an amplified negative going signal develops on the collector of all.

\* Due to positive going signal, current through Re increases and hence a positive going wave is developed across RE because of emitter follower action of will

\* ove to negative going signal on the base of 012, an amplified positive going signal develops on the collector of 802 and hence a negative going signal develops across RE because of emitter follower action of Quz

\* the signal voltages across RE, due to the effect of on and 012 are equal in magnitude & 180° out of phase.

\* Hence, these two signals cancel each other & there is no signal across the emitter registance. Hence, there is no a.c. flows through the RE.

on i.e., I.e. on Aeron \* 4 is the olp taken across collector, of our and ouz. The two olp's on collector 1 &2 are equal in magnitude but opposite polarity. No is the difference blu these two signals.

Ex: 10-(-10) = 20

\* Hence, the difference voltage, oil % is twice the voltage of single ended olp.

mode, Re does not introduce negative feedback.

In this made, the signals applied to the base of all and Out one derived from the same source. The two ilp signals one equal in magnitude and phase the circuit diagram is.

transistor our is a positive going signal since the circuits are emitter biased, the same signal voltages appear across RE, which adds together

\* Hence, RE carries a signal current and provides negative feedback. This feedback reduces the common mode gain of DA.

\* The two old signals across on and one having same magnitude and one in phase each other.

: the difference of voltage, vo is almost zero & neglibily small. But ideally it is zero.

Scanned with OKEN Scanner

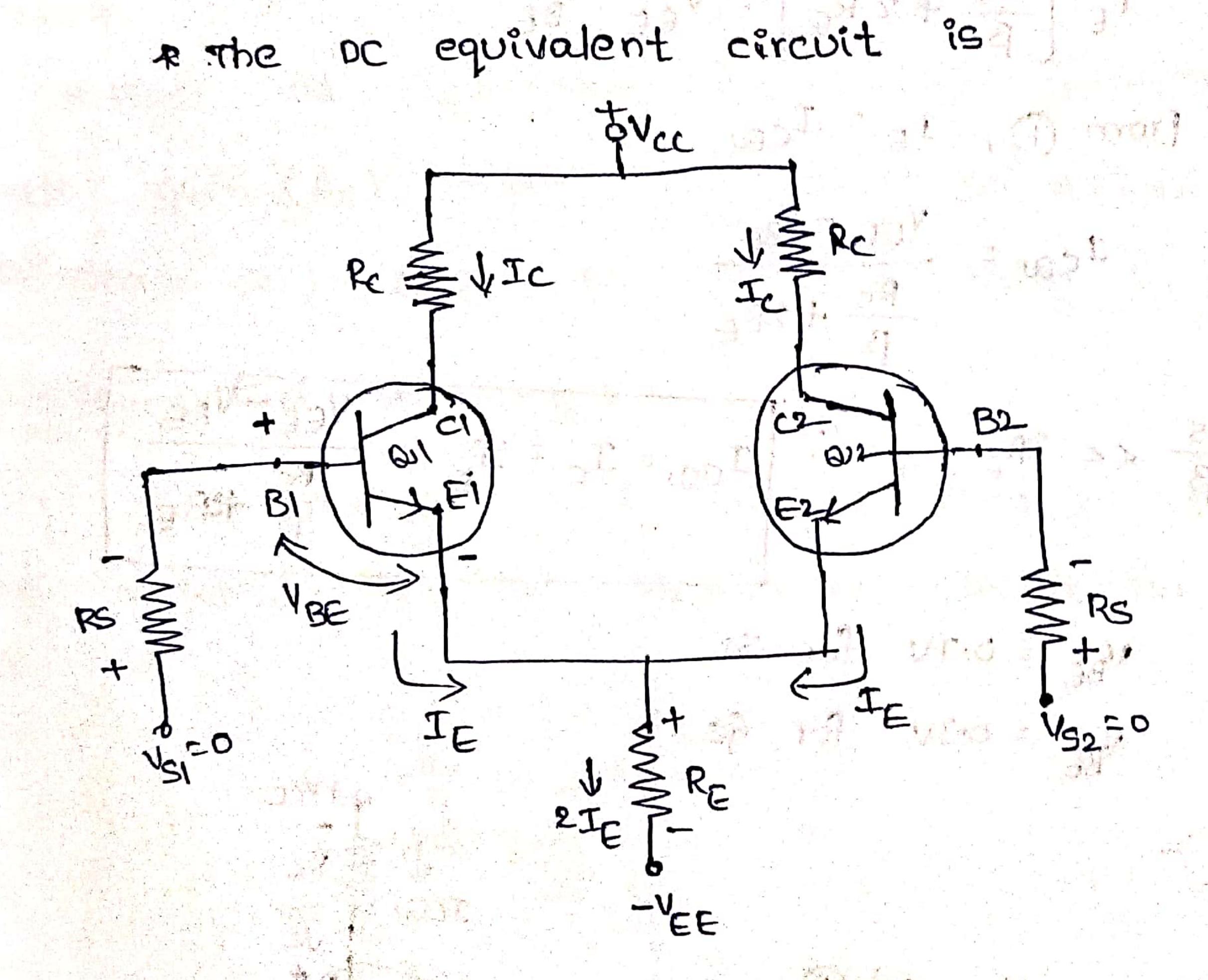

DC Analysis of Differential amplifier:

4-10-17-6-14-11

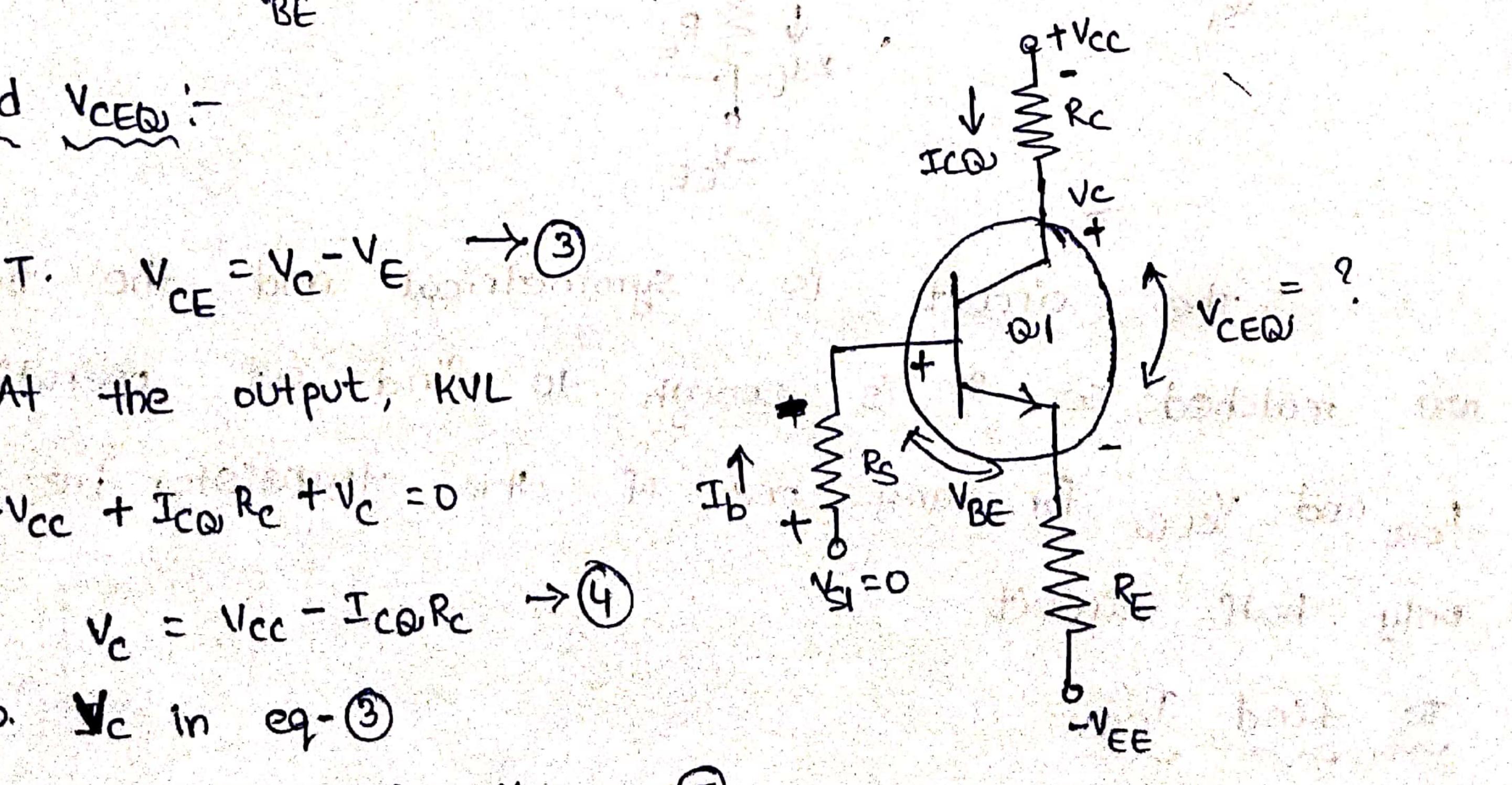

\* Dc analysis means to obtain the operating point

values i.e.; Ica & vcea for the transistors used

\* The Vcc and VEE one d.c supply voltages while the input signals one A.c.

\* The DC equivalent circuit can be obtained by reducing the ilp a.c signals to zero.

in the circuit is symmetrical and the two transistors are matched, so it is enough to find out operating point I and  $V_{CEQ}$  for any one of the transistor i.e.; consider only half circuit.

To find Ico!

Apply KVL to Base emitter loop of OI,  $-V_{SI} + I_{BRS} + V_{BE} + 2I_{ERE} - V_{EE} = O \longrightarrow (i)$ ,

W. K.T.

$$\psi_1 = 0$$

,  $\exists c = \beta \exists e$

$$\exists C \otimes \Xi \exists c \cong \exists e$$

$$\exists E = \beta \exists B \implies \exists B = \Xi E$$

$$I_E = \beta I_B \implies I_B = \frac{I_E}{\beta} \implies 0$$

Sub.

$$y_c$$

in eq-(3)

s my in when we also be the former without

none and the way

Book - ANT BUT TO

100 经决定的

YCEW = YCE = YCC - ICOVPC + YBE

-> DC Analysis is same for remaining differential Amplifiers.

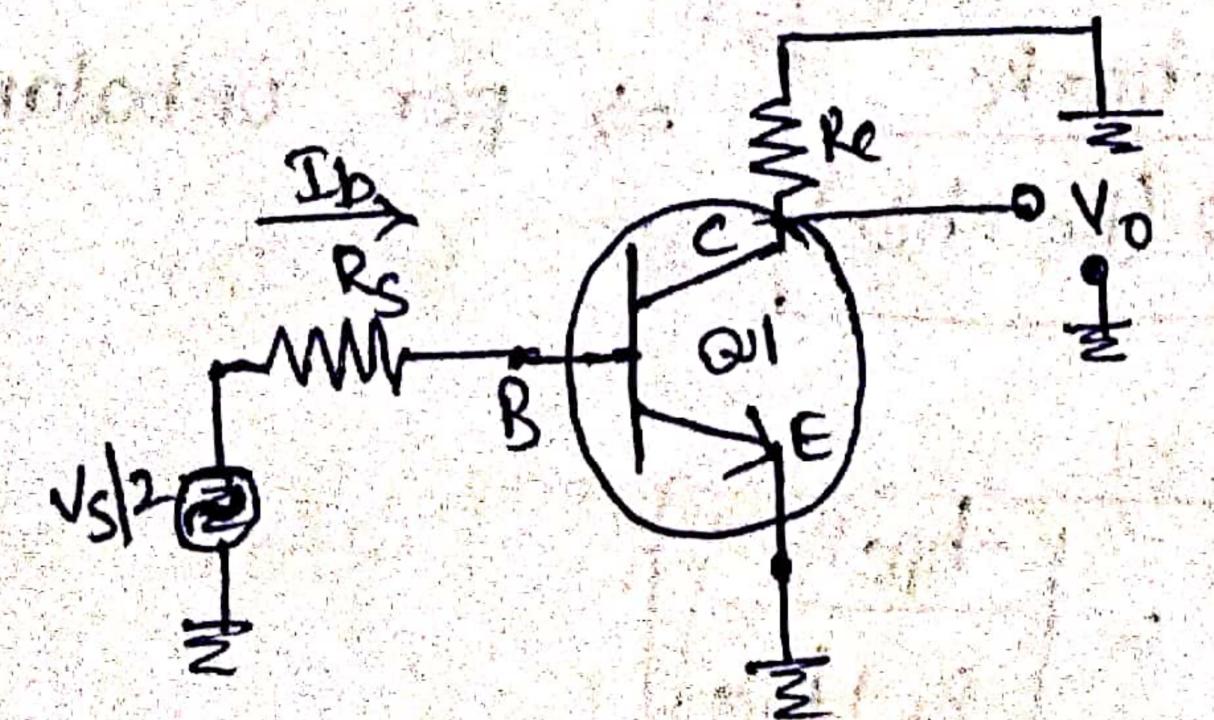

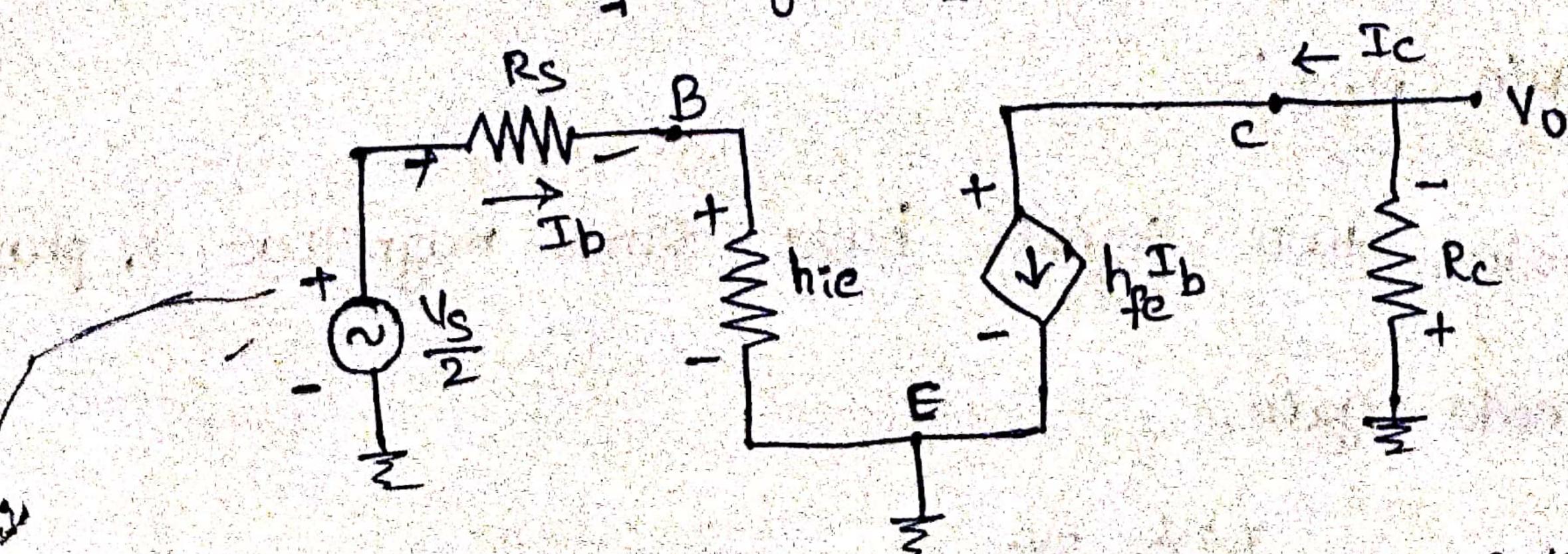

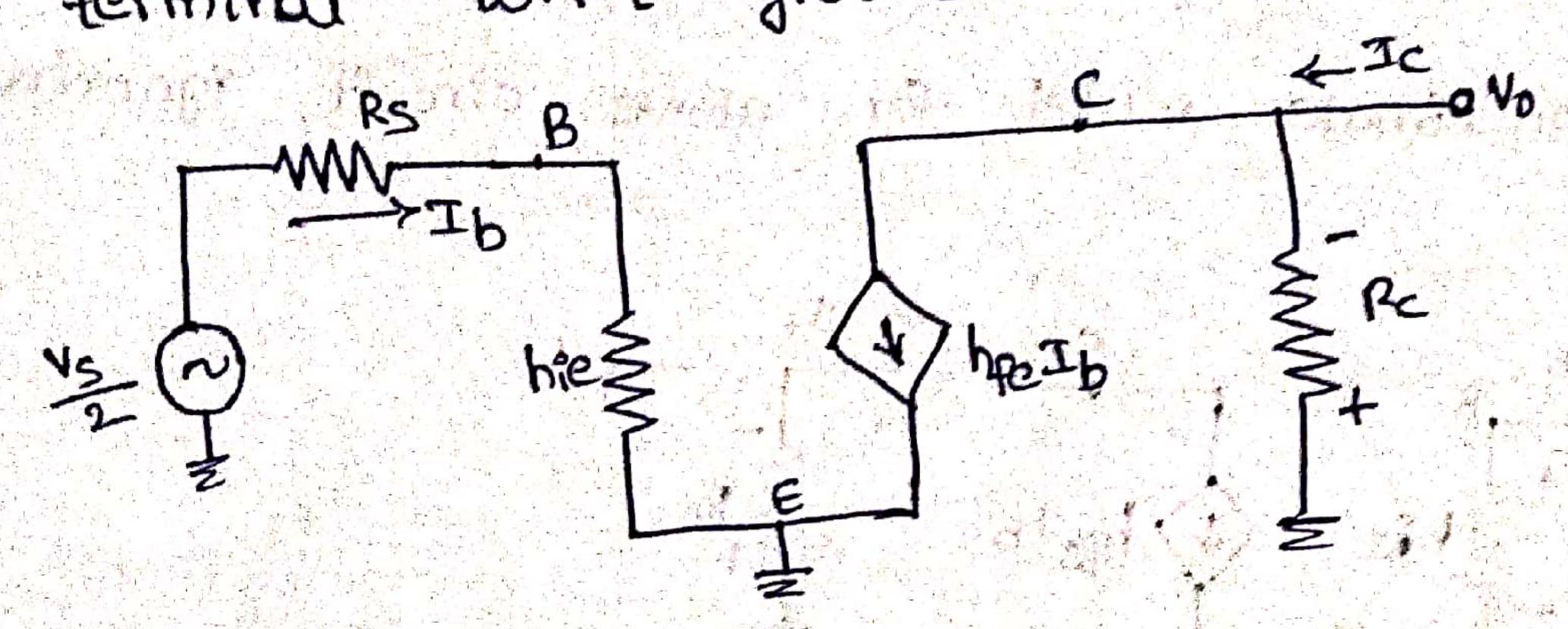

AC analysis of differential amplifier:

\* Ac analysis means consider ac signal and make de

# Two transistors were matched is consider that circuit.

\* Here we calculate differential gain (Ad), comprom mode gain (Ac), input impedance (or) resistance (Ri), output resistance (Ro), comprom the DA using h-parameters.

#### O pifferential gain (Ad):-

consider half circuit because two transistors are matched. The aic equivalent circuit for one transistor is

the appropriate hybrid model for above fig. is shown below, by neglecting him  $2h_{\infty}$ .

Here, hie = 11p impedance

here = 10p impedance

here = forward current

the reverse voltage gain

the old admillance.

Scanned with OKEN Scanne

W.K.T.

$$Ad = \left| \frac{V_0}{V_1} \right|$$

$$V_{d} = V_{1} - V_{2} = \frac{V_{S}}{2} - \left(\frac{-V_{S}}{2}\right) = V_{S}$$

$$P_d = \left| \frac{V_0}{V_S} \right|$$

output voltage, vo = -IcRc

From cercust, Ic is here Ib

$$\therefore V_0 = -h_{fe} \pi_b R_c \rightarrow 0$$

$$V_S = 2I_b(R_S + hie) \rightarrow 2$$

$$\frac{eq(0)}{eq(0)}, \frac{V_o}{V_o} = \frac{-hfe^{\pm}bRc}{2\mp b(R_s+hie)}$$

$$Ad = \frac{|Vo|}{|Vs|} = \frac{-he}{2(Rs+hie)} \Rightarrow For unbalanced olds$$

for balanced olp,

Fall balanced of = 2 Add unbalanced of p.

\* In this mode, two signals have same magnitude & phase.

the common mode gain,

Ac =

$$\frac{V_0}{V_C}$$

| but  $V_C = \frac{V_1 + V_2}{2} = \frac{2V_S}{2} = V_S$

Scanned with OKEN Scanner

the approximate model for above circuit, ignoring

the old voltage is given by, vo = -Ierc

From circuit, Ic=KieIb

Apply KVL at Up loop,

$$V_S = I_b(R_S + hre^{\frac{1}{2}R_E} + 2R_E + 2R_E hre^{\frac{1}{2}R_E}) \rightarrow 2$$

$$\frac{e_{9}\cdot 0}{e_{9}\cdot 0} \Rightarrow \frac{V_{6}}{V_{8}} = \frac{-h_{fe}}{T_{b}\left(R_{5} + h_{fe} + 2R_{E}\left(1 + h_{fe}\right)\right)}$$

balanced & unbalanced ofp.

3) ille impedance :-

the ilp impedance is measured at any one of the ille ferminal wirt ground.

$$R_1 = \frac{\sqrt{2}}{2} I_b$$

The

$$\frac{VS}{2b} = \frac{VS}{2(RS+hie)}$$

$$R_{\circ} = \frac{y_{s}}{2}$$

$$\frac{y_{s}}{2(R_{s}+hie)}$$

$$R_1 = R_S + hie$$

For single input, RI = Rsthie For dual input, RI = 2 (Rs+hie)

impedance: output

the old impedance of the circuit is measured olb mit ground.

potpot impedance, Ro=Rc.

W. N.T. CMRR =

$$\frac{Ad}{Ad}$$

Relation Ac Relation Relations for dual file and  $Ad = \frac{Rchie}{Rs+hie}$  is  $Ac = \frac{Rchie}{Rs+hie}$  is the set of t

Rethret 2Re (14hpe)

Rethret Rethre

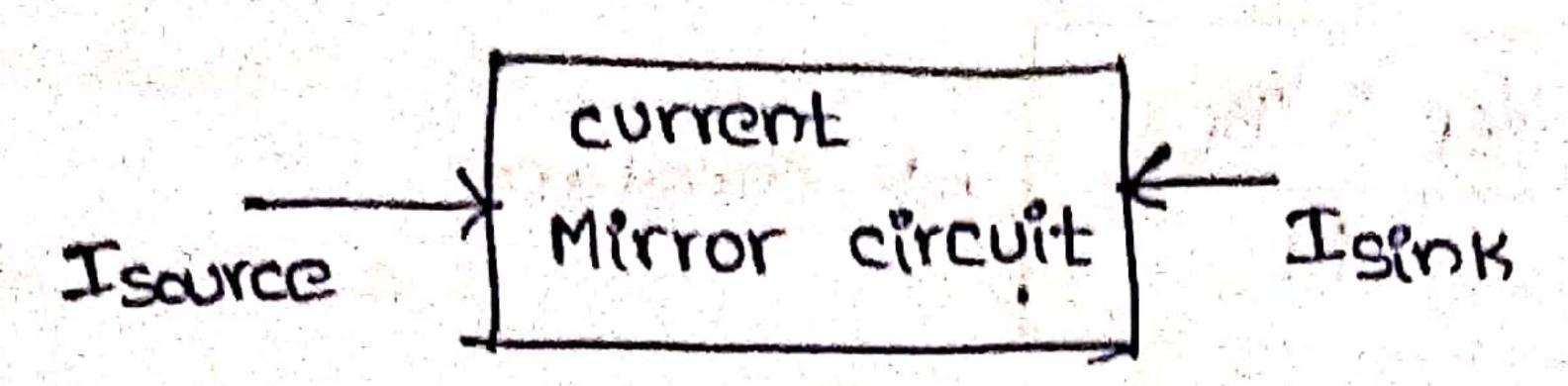

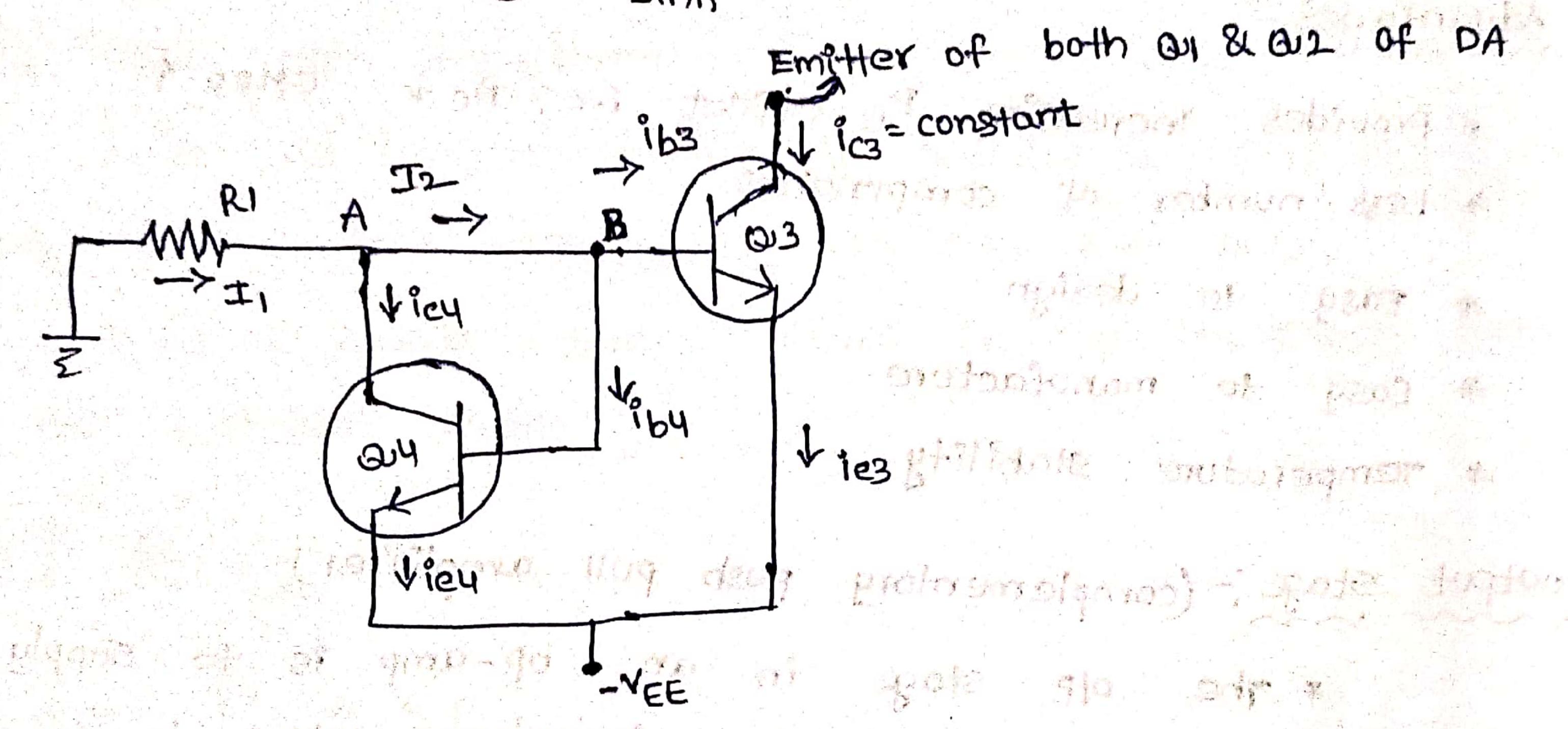

mirror "Current

> merror cercult means, old current current

image of current.

= constant.

03, Ou une matched transistors.

KCL at node A.

$$T_1 = T_2 + i_{CY} \rightarrow \odot$$

KCL at node B,

$$\pm_2 = i_{b3} + i_{b4}$$

$$\pm_2 = 2i_{b3} + i_{b4}$$

\*: From (1)

$$T_1 = \frac{2ic3}{\beta} + ic3$$

$$T_1 = ie3 \left(-\frac{2}{\beta} + i\right)$$

Since

$$\beta$$

is very high,  $\frac{\pi}{\beta}$  is ignored

kul of was transistor

#### Advantages:

- \* provides increasing RE effect i.e.; Ac & CMRR 1

- \* Less number of components.

- \* Fasy to design

- \* Easy to manufacture

- a remperature stability.

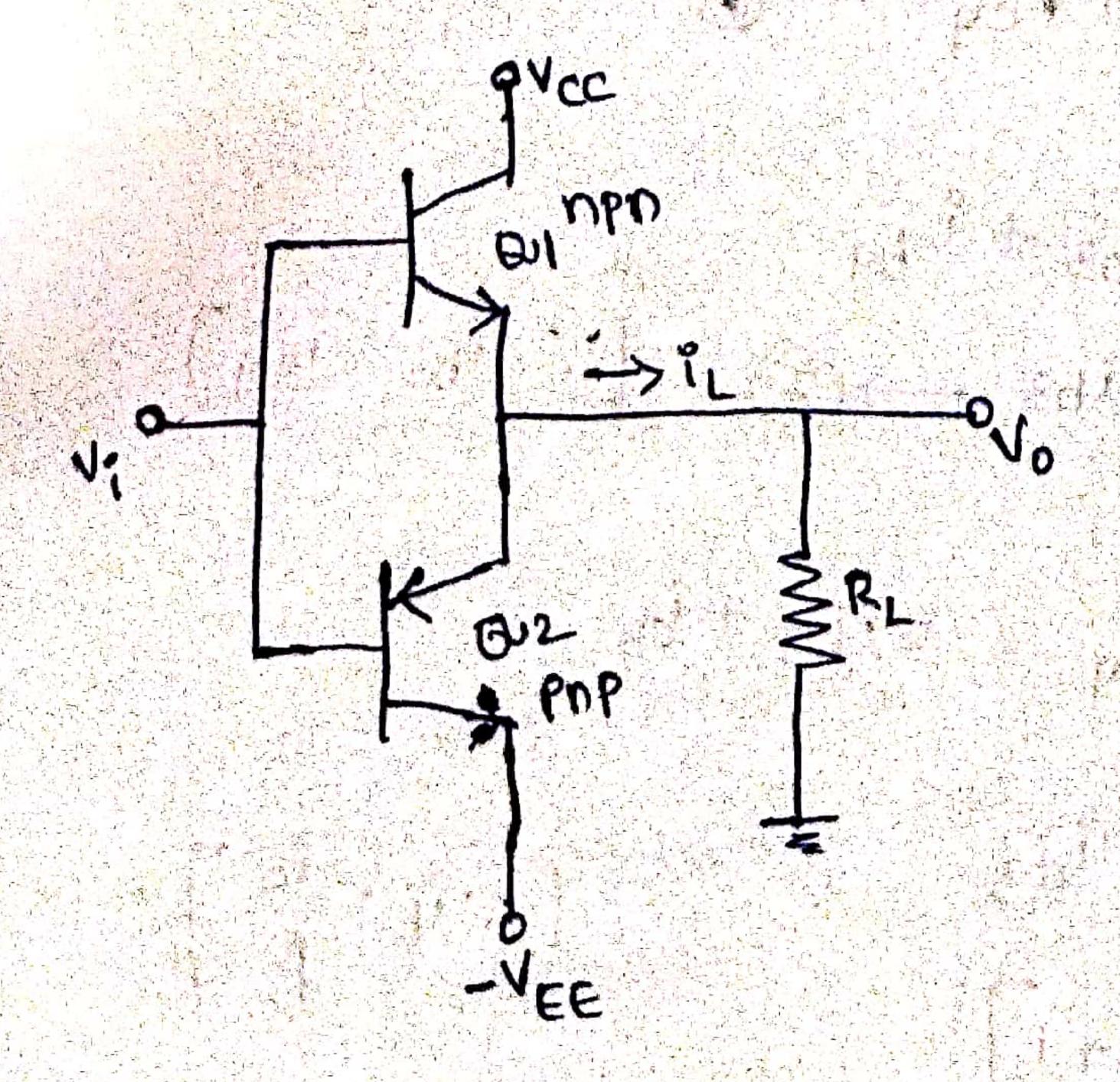

output stage:- (complementary push pull amplifier)

# The olp stage in an op-amp is to supply the load current & provide a low impedance olp. ideally the total supply voltage is . Vcc + VEE:

transistors Oi (npn), and Oi=(pnp) connected as shown in fig.

fig :- complementary stage of DA

-YEE signolp stage of 10741

Scanned with OKEN Scanner

is on and supplies current For Vi positive, ou load RL'

For Up negative, Oil is cut-off & oil acts as a

to remove current from load RL.

the old vo remains 29 in this The limitation zero until the ilp vi exceeds VBE (cut in) = 0.5 V. This is called a cross over distortion)

\* It can be eliminated by applying a bias voltage V slightly greater than 2 VBE(CUT-in) = IV blw two bases.

of so, a smoull current flows in the transistors even en the quiescent state.

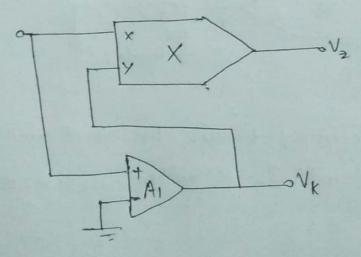

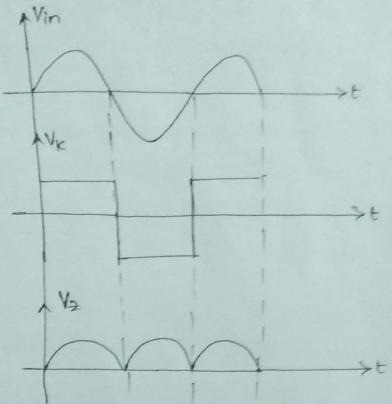

out of phase \* If V=0, then No is 180°

signal V2 \* If V2=0, then vo will be inphase with

signal applied at

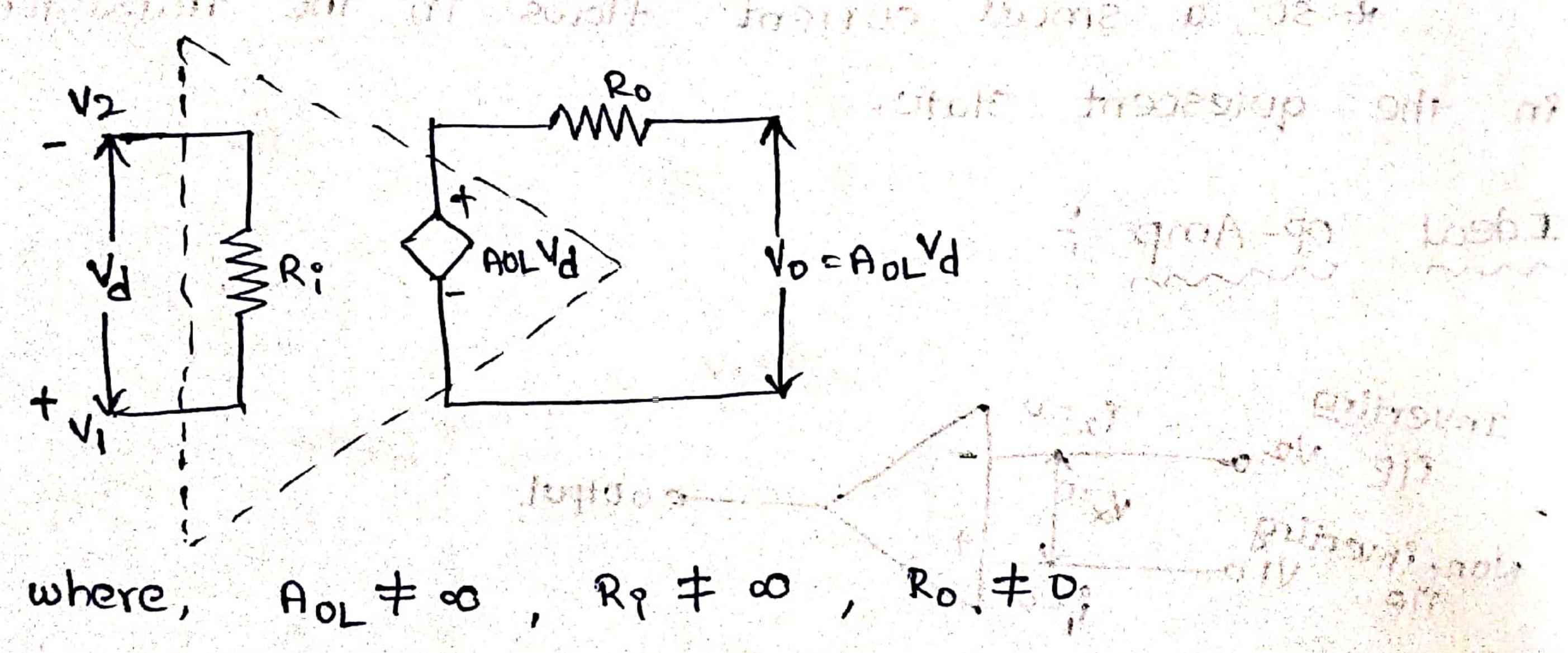

\* The ideal op-amp characteristics are

1. open 100p voltage gain (AoL) = 00

2. Input registance, Ri = 0

3. old resistance, Ro = 0

4. Bandwidth = 00

5. offset voltage = 0

(28)

# Because of  $\infty$  input impedance, the ideal op-amp draws no current at both the ilp terminals. i.e.;  $l_1 = l_2 = 0$ .

# since gain is infinity, the differential ilp voltage between inverting & non-inverting terminal,  $V_1 = V_1 - V_2$  is zero for finite olp voltage.

\* The olp voltage  $V_0$  is independent of the olf current as  $R_0=0$ . Thus olf can drive infinite not of other devices.

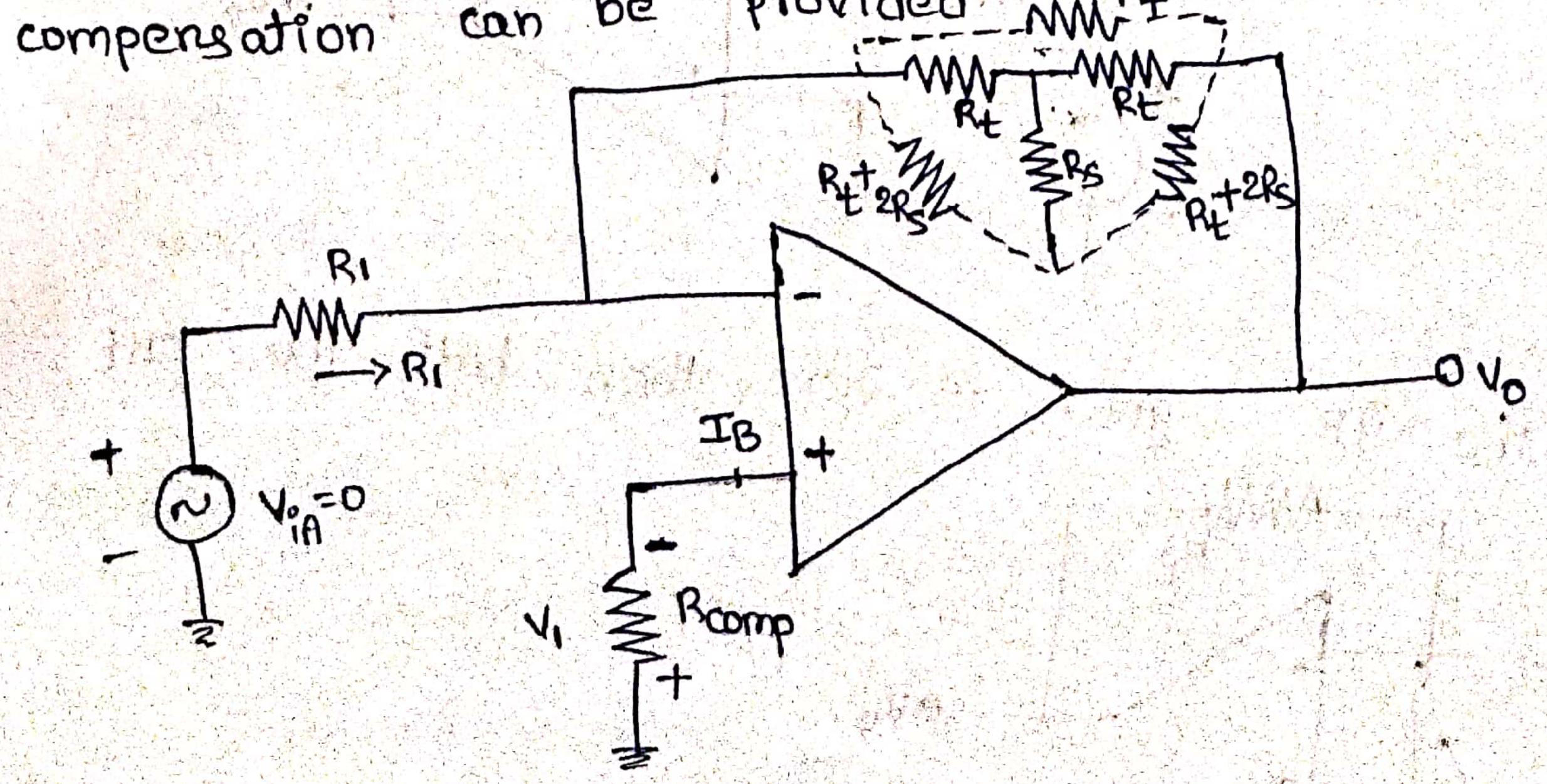

The physical op-amp is not an ideal one, the equivalent direvit is

Here, the olp is a voltage controlled voltage source, Aol Vd is the equivalent thevinen voltage, source.

Ro is the equivalent thevinen resistance.

: of voltage,  $N_0 = A_{0L} \cdot V_0$   $V_0 = A_{0L} \cdot (V_1 - V_2)$ where,  $V_0 = Op$  Voltage  $A_{0L} = Open \quad loop \quad gain$   $V_1 = differential \quad voltage.$

Scanned with OKEN Scanner

saturation

-0 Vo=(V1-V2)

--a the rate bearing from ----- der en line and Transfer ideal o make annual and the statement of descriptions and the co or had have who is the said to be a state of and that is designed for the latest and the first when a work do need dollars were gain loop infinite. Thus many the series of the series are processing and a street training street the always

> V, >V2 then Vo = + Vsat If  $V_1 < V_2$  then  $V_0 = -V_{SQd}$ .

\* The olp assume one of the possible states, î.e. +Vsat (or) -Vsat and olp

level, i.e. ± vsod.

and the same time became whose a new

acts as a switch.

±Vsod = ±Vcc

voltage transfer characteristics of practical op-amp; can be greatly increases an op-amp to phility of providing a -ve feedback.

\* The old in this stage is not drives into saturation circuit becomes linean manner

Aa 85 -finite - for op-amp 1410 \*practically the 5×102 Vo = Aol Vd + Vsat = 2×105 V4 ±15V saturation voltages are ideal characteristics Practical ideal Symbol parameter S.NO op-amp. op-amp Jain JUZI 0 output impedance 2 2 M.I ilp impedance Roza 0 11p offset current 20nA Tios 4. MV Voltage O ilp offset Vios 5, **4**3 IMHZ B.W Bandwidth 6. 90dB 00 CMRR

Scanned with OKEN Scanne

9 ill bias current IB 80nA

rejection ratio

PSRR

O 30.UV/V

#### Dic characteristics of op-Amp :-

Dc characteristics means to find

1 Input blas current (IB) (2) Input offset voltage (Vios)

3) Input offset current (Ins) (9) Thermal drift

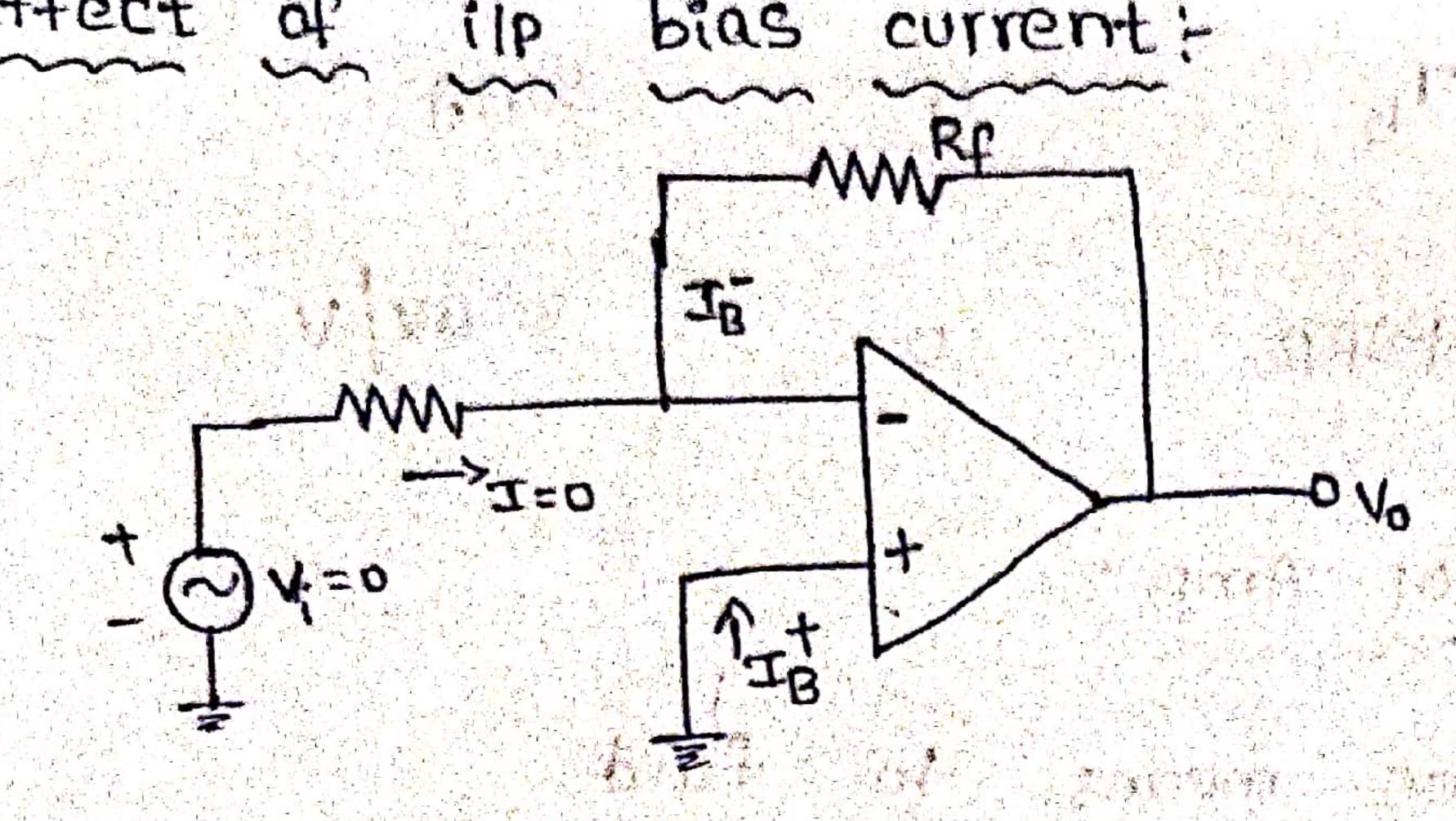

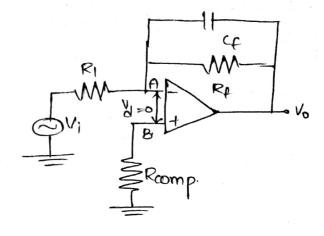

#### D'Input bias current (IB):

\* the ideal op-amp ilp terminals does not drawn any current because of infinite ilp impedance.

\* The ilp stage of the op-amp is the dual ilp DA and the ilp terminals one the base terminals of the two transistors.

\* whenever both the ilp terminals of an op-amp are grounded, Ideally the olp Voltage should be dero thowever in this condition op-amp shows a small olp voltage. This is due to mismatching present in the internal circuit of an op-amp.

\* the mismatching in the transistors are because, of the current present in the ilp terminals.

\* The average value of the two currents flowing into the op-amp ilp terminals called input bias current and denotes as IB

$$T_{B} = \frac{T_{b1} + T_{b2}}{2}$$

where,

$$T_{B} \text{ is temperature dependenting } T_{b2}$$

Scanned with OKEN Scanne

Scanned with OKEN Scanner

The olf. voltage is given by  $V_0 = T_B K_f$

>> for ICT41 op-amp, the ilp bias current is 80 nA, for BJT the Value of resistance is IMIL

$V_0 = I_B R_2$

= Bona XI-MA-;

$V_0 = 80 \text{my}$

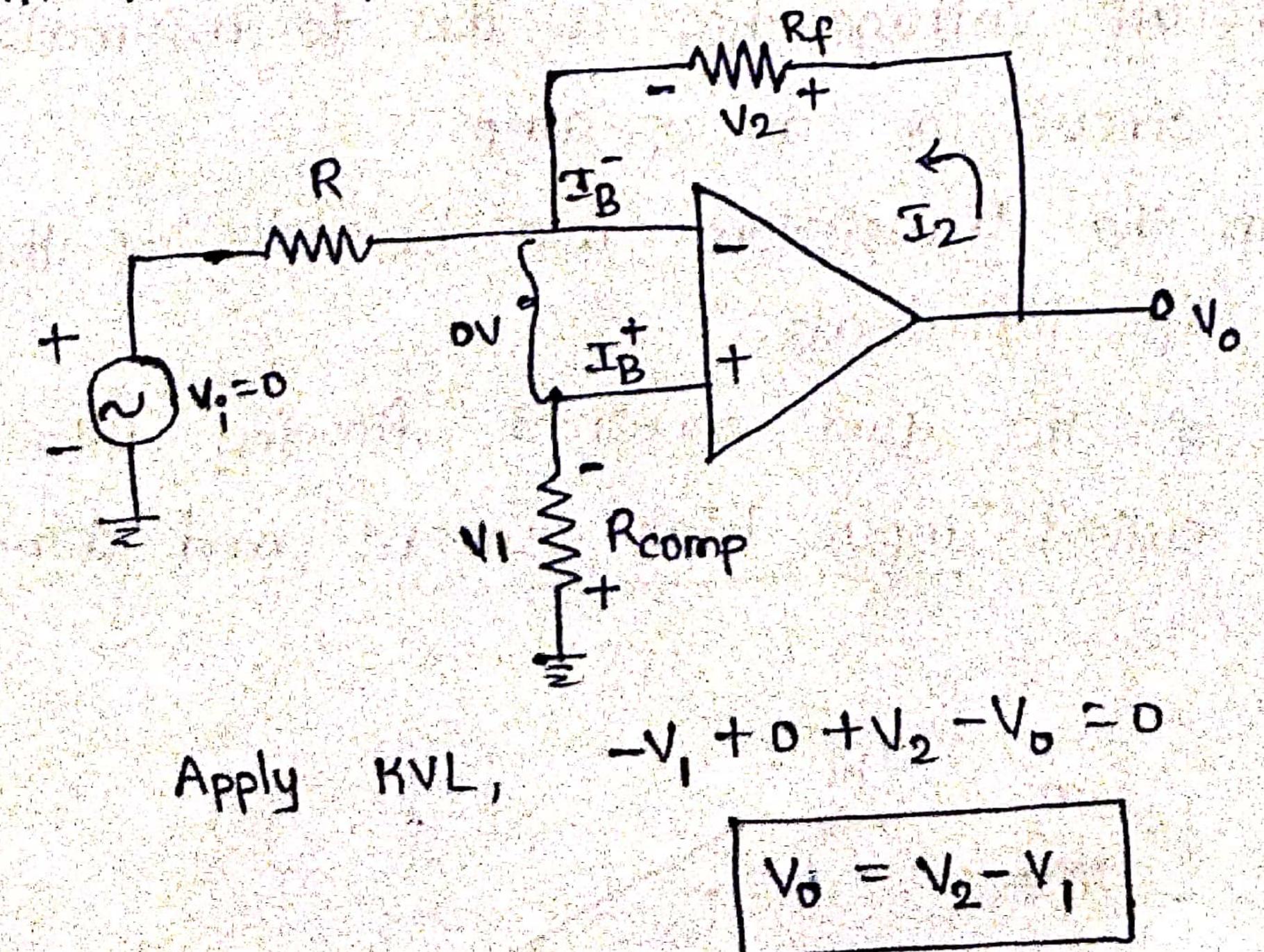

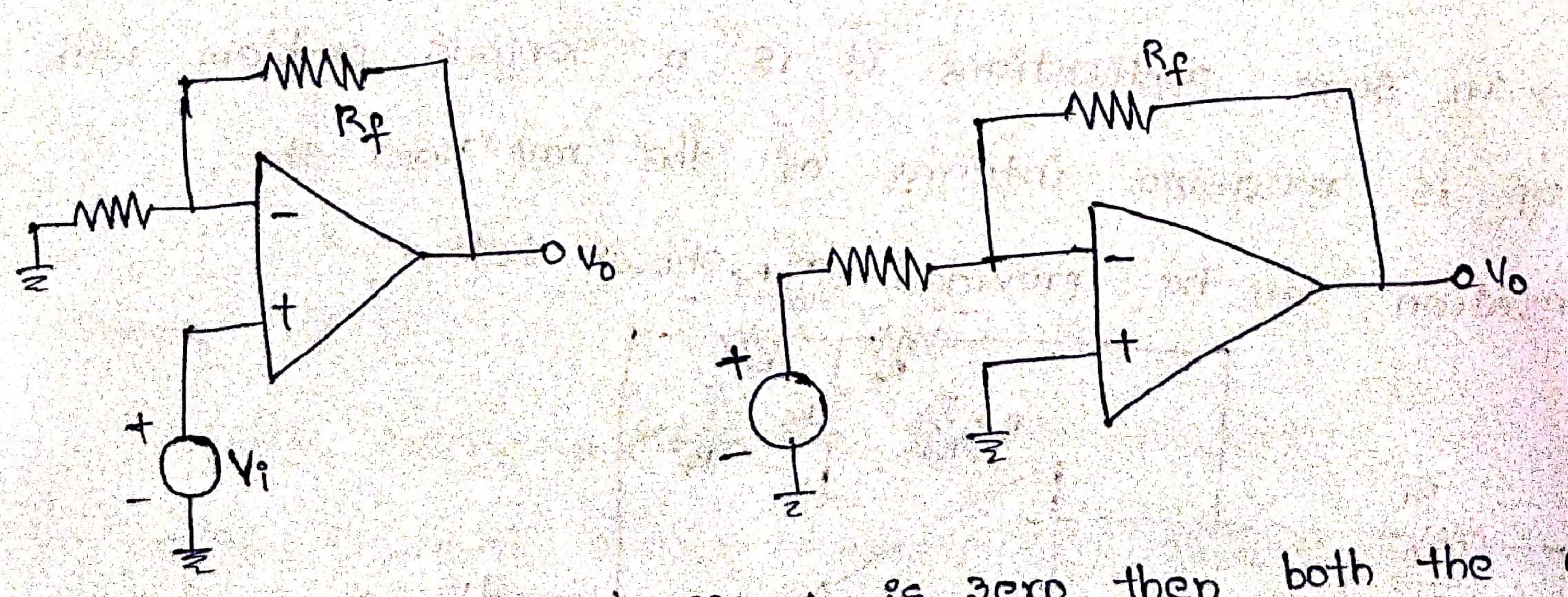

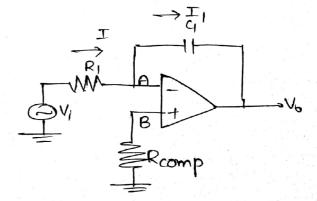

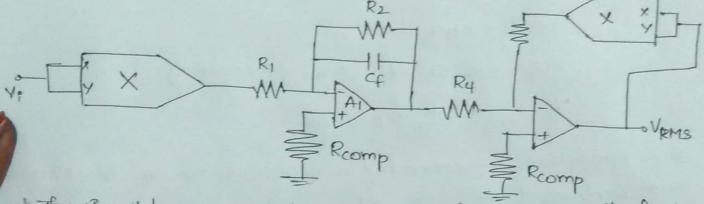

For zero ilp. signal, the olp also must be zero but due, to the ilp bias current the olp voltage is 80mV. In mv. This becomes the serious issue. Now the problem can be rectified with the help of compensation resistor Rcomp.

$\rightarrow$  For proper value of  $R_{\rm f}$  the value of  $V_2$  is get concelled with VI and makes the oil as sero.

perivation of Rome resistor t

In generally, we one assuming that  $\left( \mathbf{I}_{B}^{\dagger} = \mathbf{I}_{B}^{\dagger} \rightarrow \mathbf{O} \right)$

$$\frac{N}{R_{comp}} = I_B^+ - NC$$

$$T_2 = \frac{V_2}{R_2} \implies (5)$$

$$W\cdot K\cdot \tau \cdot v_0 = v_2 - v_1 \longrightarrow 0$$

Now , for viso then voso

$$V_2 = V_1 = 0$$

$$V_2 = V_1 \longrightarrow 0$$

8),(9),(3)

$$T_{B} = \frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{F}} = V_{1} \left( \frac{R_{F} + R_{1}}{R_{1}R_{F}} \right) \xrightarrow{\sim} (9)$$

(9).(2) in (1)

$$\mathcal{I}_{B}^{+} : \mathcal{I}_{B}^{\bullet} \Rightarrow \frac{\mathcal{N}_{I}}{R_{COMP}} : \mathcal{N}\left(\frac{R_{I} + R_{F}}{R_{I}R_{F}}\right)$$

$$R_{comp} = \frac{R_1 R_2}{R_1 + R_2} \implies (6)$$

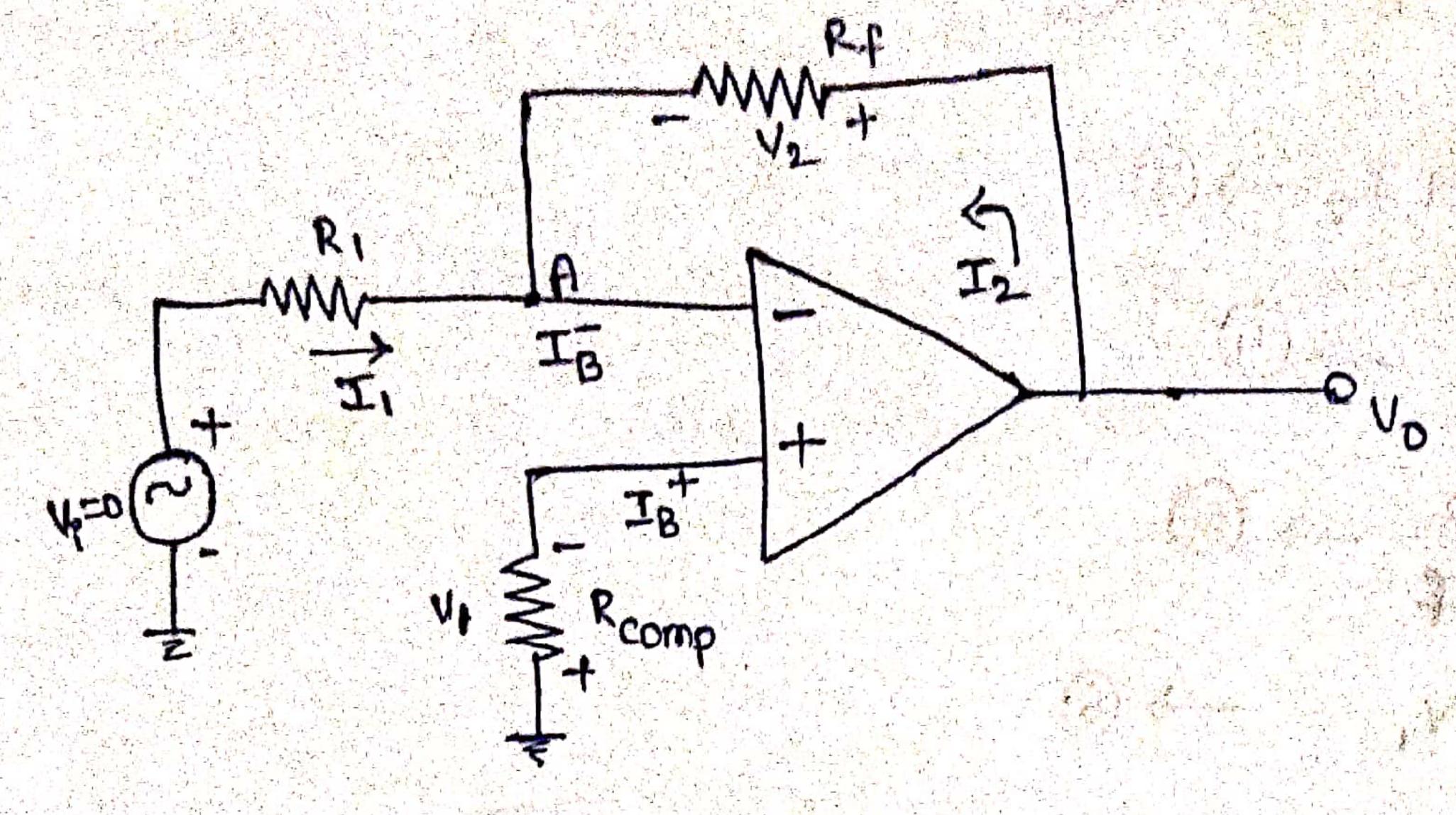

Enput offset current (Fios) in

Bias current compensation will work only when  $I_B^+ = I_B^-$ . But practically those 2 are not equal and the amount of difference blu  $I_B^+$  and  $I_B^-$  is called input offset current

the Up offset current is

Now let us excamine the effect of 11P offset current.

the old voltage of the above CKt, is,

$$N_0 = I_2R_p - N_1 \rightarrow 0$$

$$V_1 = I_B^{\dagger} R_{comp} \longrightarrow (2)$$

Apply KCL at mode 'A'

$$\pi_0 = \pi_0 - \pi_1 \rightarrow 0$$

$$\pi_1 = \frac{4}{8} \rightarrow 0$$

Sub. 2 in 9

$$T_{B} = \frac{T_{B}^{\dagger} R_{comp}}{R} \longrightarrow 6$$

(6) in (3)

$$T_2 = T_0^2 - \frac{T_0^2 R_{comp}}{R_0} - 2C$$

(3), (2) in (3)

$$V_0 = \left( \frac{T_B^+ - \frac{T_B^+ R_{comp}}{R_I} - \frac{T_B^+ R_{comp}}{R_I} \right) R_0 - \frac{T_B^+ R_{comp}}{R_I} - \frac{1}{2} \left( \frac{1}{R_I} \right)$$

To design a 7 network we first pick up

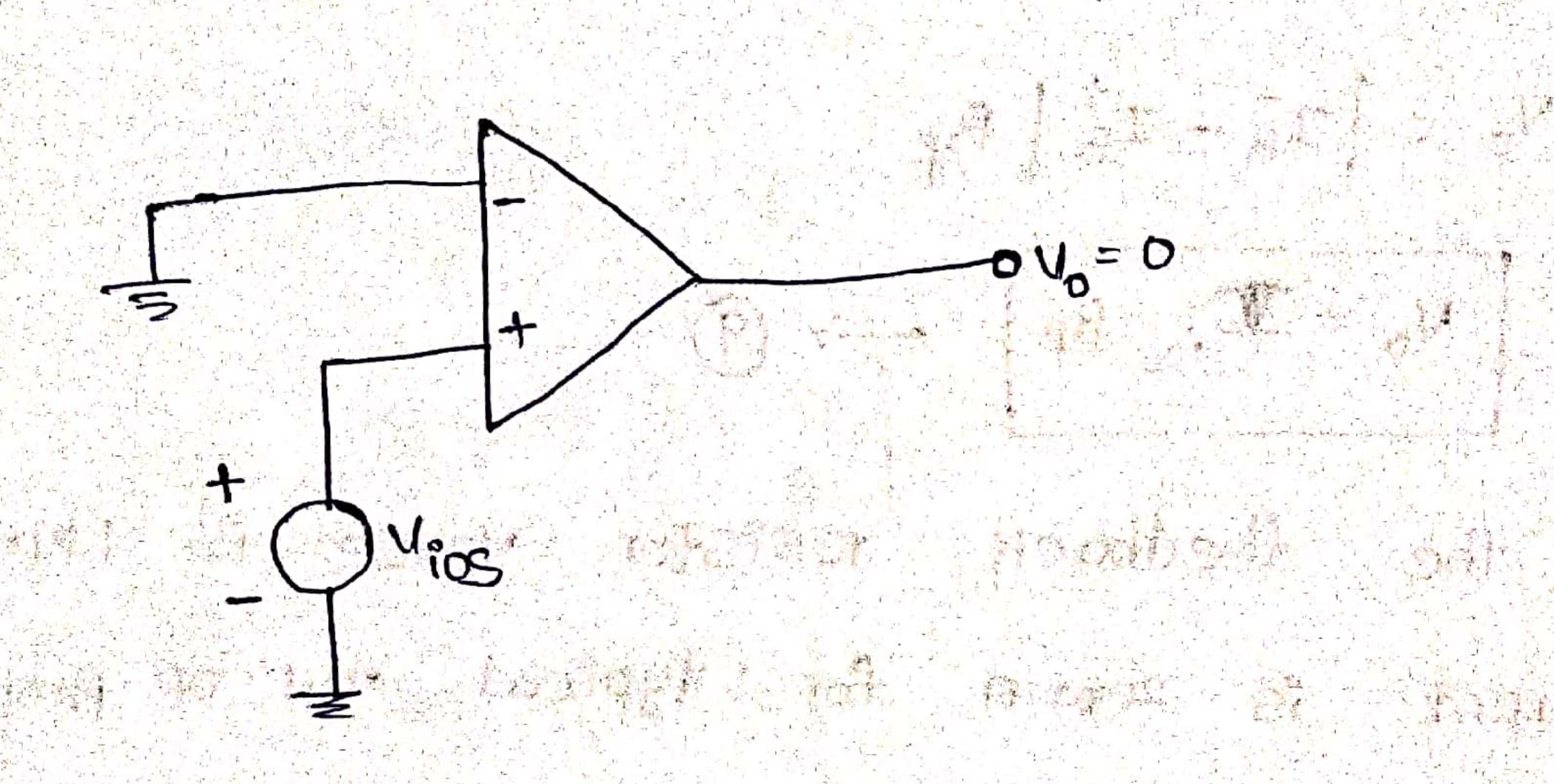

## Input offset Voltage (Vias)

\* Even though we one providing the compensation small amount of the olp voltage due to there cocist in balance in the op-Amp. unavailable

\* to bring the oil voltage as zero we are small amount of ilp voltage at either terminals of op-Amp is called (Vios) and it is shown as below.

Let us examine the effect of the offset voltage inverting and non-inverting op-Amp as follows.

Signal is zero, then both the

when becomes

W.K.T.

$$R_{comp} = \frac{R_1 R_p}{R_1 + R_p} \longrightarrow (8)$$

sub. (8) in (9)

$$V_0 = I_B - \frac{\left(\frac{R_1 R_f}{R_1 + R_f}\right)}{\left(\frac{R_1 R_f}{R_1}\right)} I_B^{\dagger} - I_B^{\dagger} \left(\frac{R_1 R_f}{R_1 + R_f}\right)$$

$$R_1 V_0 = IBR_1 - \left(\frac{R_1 R_P}{R_1 + R_P}\right) IB - R_1 IB \left(\frac{R_1 R_P}{R_1 + R_P}\right)$$

$$= \left( T_B - T_B \right) R_f$$

If the feedback resistor value is IMA and ilp offset current is 200nA for typical 741 OP-Amp using BIT then the OIP, voltage is

$$\sqrt{V_0} = 200 \text{ mV}$$

The some applications it is a serious problem with the olp is measure interms of the mv how the compensation can be provided as reshown below.

Now the designing of the CKt for the Compensation is as follows:

From the circuit, the voltage  $V_2 = V_0 \frac{R_1}{R_1 + R_2} \rightarrow 0$

$$V_{2} \left( \begin{array}{c} R_{1} + R_{F} \\ \hline R_{1} \end{array} \right) = V_{0}$$

$$R_{1}$$

$$V_{0} = V_{0} \left( \begin{array}{c} 1 + \frac{R_{F}}{R_{1}} \\ \hline R_{1} \end{array} \right)$$

From circuit,

$$V_{ios} = |V_1 - V_2|$$

$$= |0 - V_2|$$

$$= |-V_2|$$

$$V_{ios} = V_2 \longrightarrow 3$$

$$V_0 = V_{ios} \left(1 + \frac{R_f}{R_1}\right) \longrightarrow 4$$

thermal Drift:

\* Drift means a function of temperature.

# Bias current, offset current and offset voltage changes with temperature.

\*A circuit carefully hulled at 25°C may not remain when the temperature rises to 35°C. This is called drift when the

- # an offset current drift is expressed in najoc.

- \* An offset voltage drift is expressed in mule.

- \* This indicate the charge in offset for each degree celsius charge in temperature.

- # There one very few circuit techniques that can be used to minimize the effect of drift.

- \* Forced air cooling may be used to stabilise the ambient temperature.

A.C characteristics of op-Ampi-

the important A.c. characteristics of op-Amp one

1. Frequency response 2. Slew Rate.

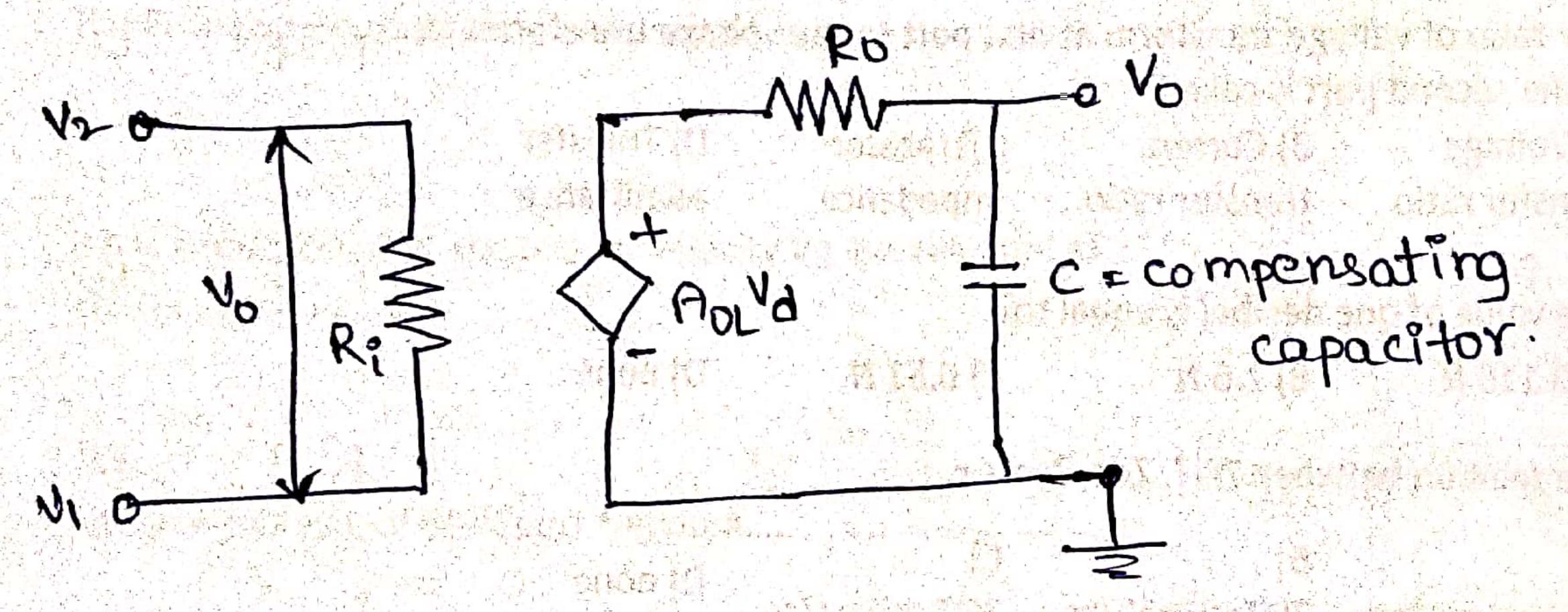

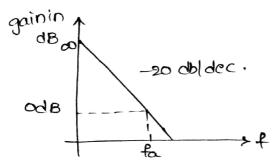

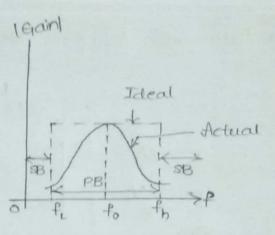

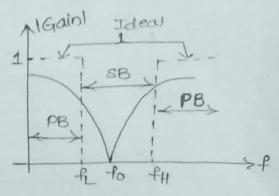

## 1. Frequency response :

For ideal op-amp the bandwidth is a that means the gain is constant upto infinity but for practical op-amp the gain decreases as the frequincreases.

Let -ixc be the capacitive reactance due to capacitor. From the above fig. to get Vo. apply voltage division rule "V"

$$V_{o} = A_{o}V_{d}\left(\frac{-3x_{c}}{R_{o}-3x_{c}}\right)$$

$$\mathbf{W} \cdot \mathbf{K} \cdot \mathbf{T}$$

.  $-\mathbf{j} = \frac{1}{2}$   $/ \times_{\mathbf{C}} = \frac{1}{2\pi f \mathbf{c}}$

let

$$A = -1$$

2.  $\pi_{0}C$

The magnitude of

$$A$$

is

$$\left\{A_{0L}\left(f\right)\right\} = \frac{A_{0L}}{\sqrt{1+\left(f\right)\left(f\right)}}$$

the phase angle & of A is

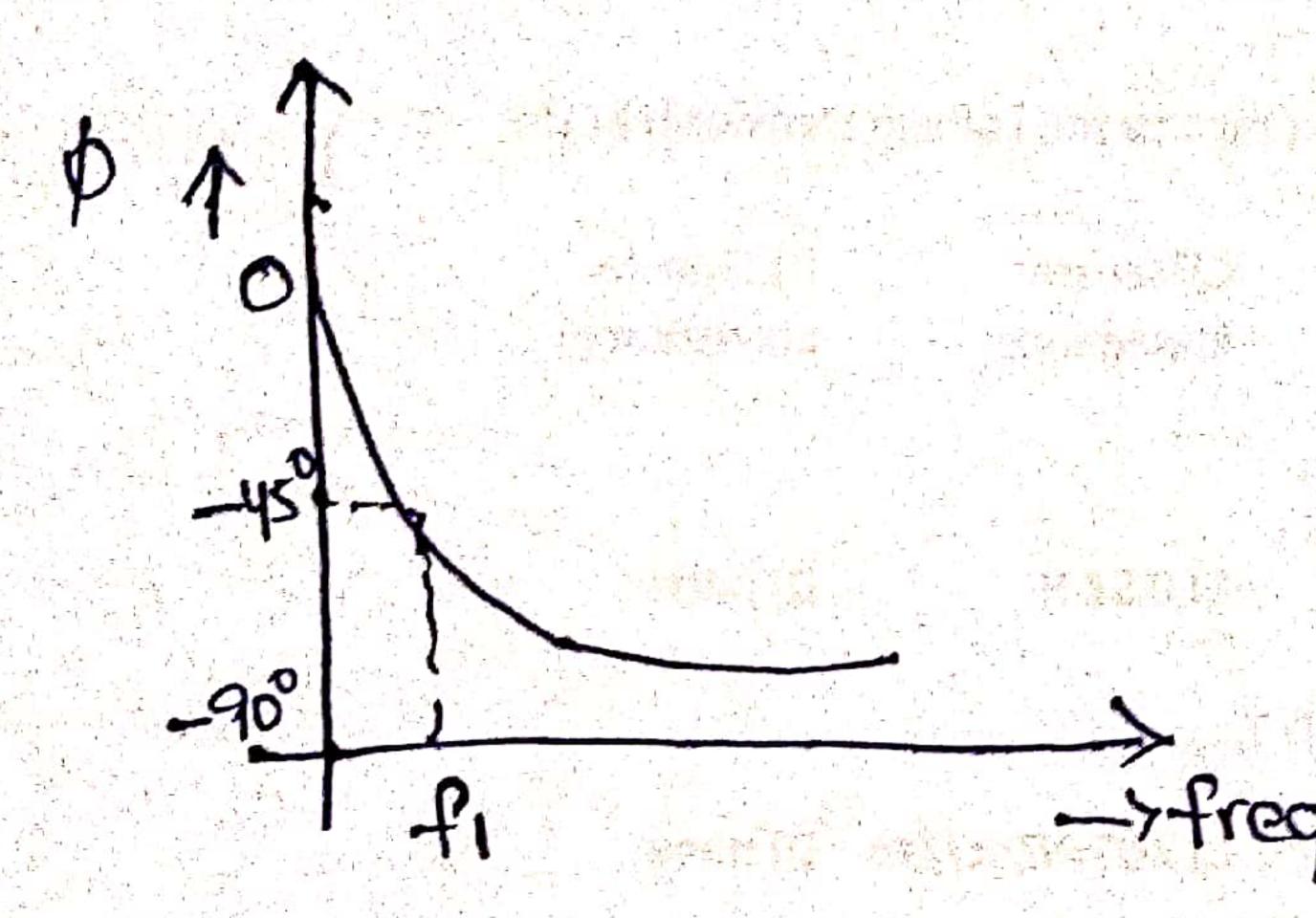

$$\phi = -\tan^{-1}\left(\left(f|f_{1}\right)\right)$$

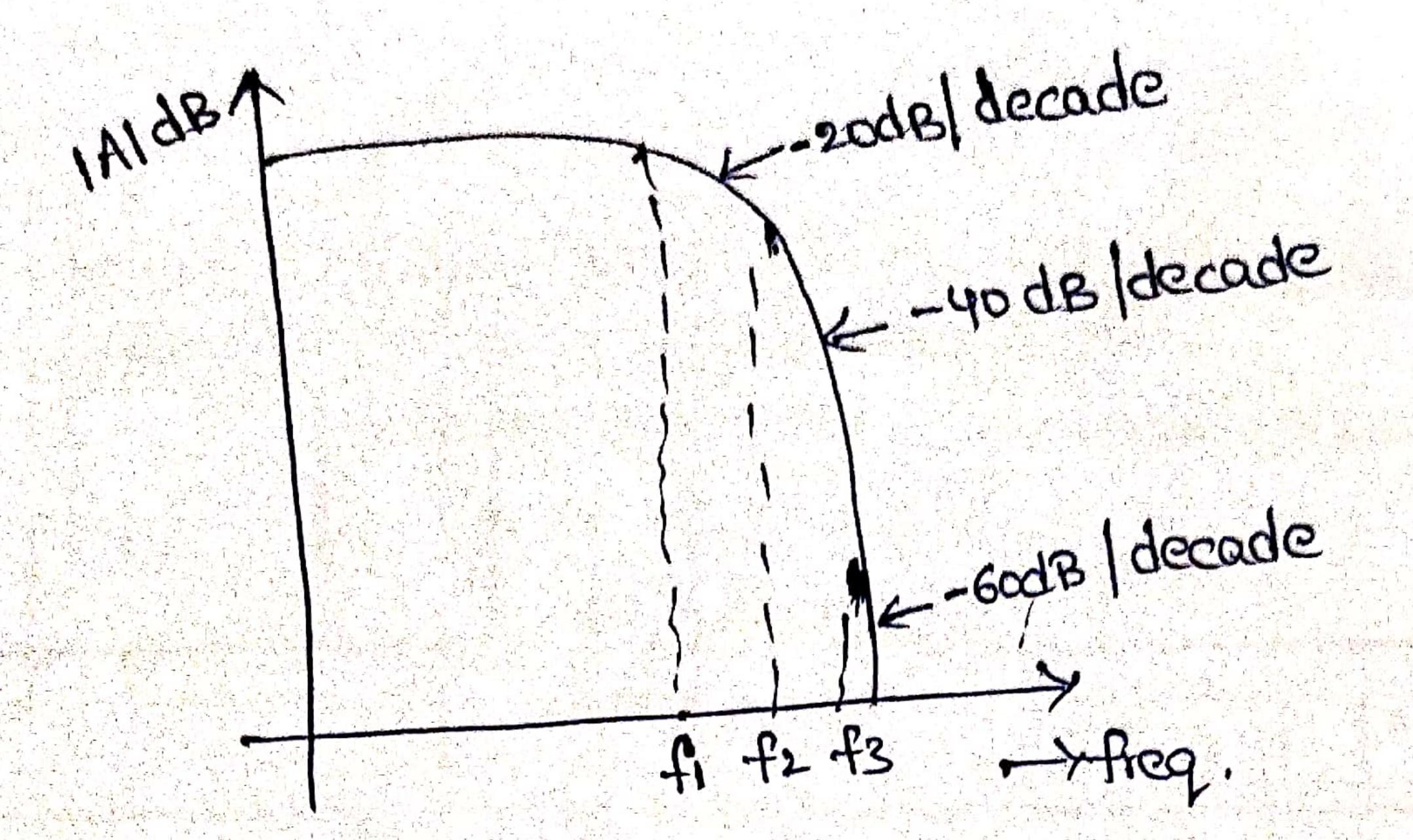

-> from the magnitude it can be seen that

(3) for the freq f<fi

the magnitude of gain is 20 log AoL in dB

(ii) At the freq f=f1

The gain is 3dB down from the dc value of AoL in dB. Thus the freq. fi is called "corner freq" (or) "center/break freq."

(iii) for the freq f>>fi)

the gain roles of at a rate of -2001B for decay.

-> the magnitude response is

freq,

Roll off

$\rightarrow$  It can further we can seen from the phase charact-eristics.

$$\phi$$

is -45° at  $f = f_1$

$$\phi$$

is  $-90^{\circ}$  at  $f=\infty$

the phase characteristics is shown below

$\rightarrow$  the voltage transfer function in S. abmain can be written as

the s-domain s=jw

→ A practical op-Amp has no of stages and each stage a capacitive component that transfer function of an op-Amp with 3 break frequency can be assumed as.

$$\theta = \frac{1}{(S+\omega_1)(S+\omega_2)(S+\omega_3)}$$

Slew Rode !-

the slew rode is defined as the miximum rode of change of old voltage with time. Usally the slew rate is expressed in VIMs and is given by

slew rade,

$$S = \frac{dV_0}{dE} \Big|_{max}$$

\* The skw rate is caused due to limited charging of the compensating capacitor and current limiting.

\* saturation of internal stages of an op-amp when a high freq longe amplitude signal is applied.

\* The internal capacitor voltage can not charges inustaneously and is given by

"For large charging rate capacitor should be small (or) charging current should be large. Hence the slew rate for the op-amp whose maximum internal capacitor changing current is known can be obtained as.

Cleus mate:

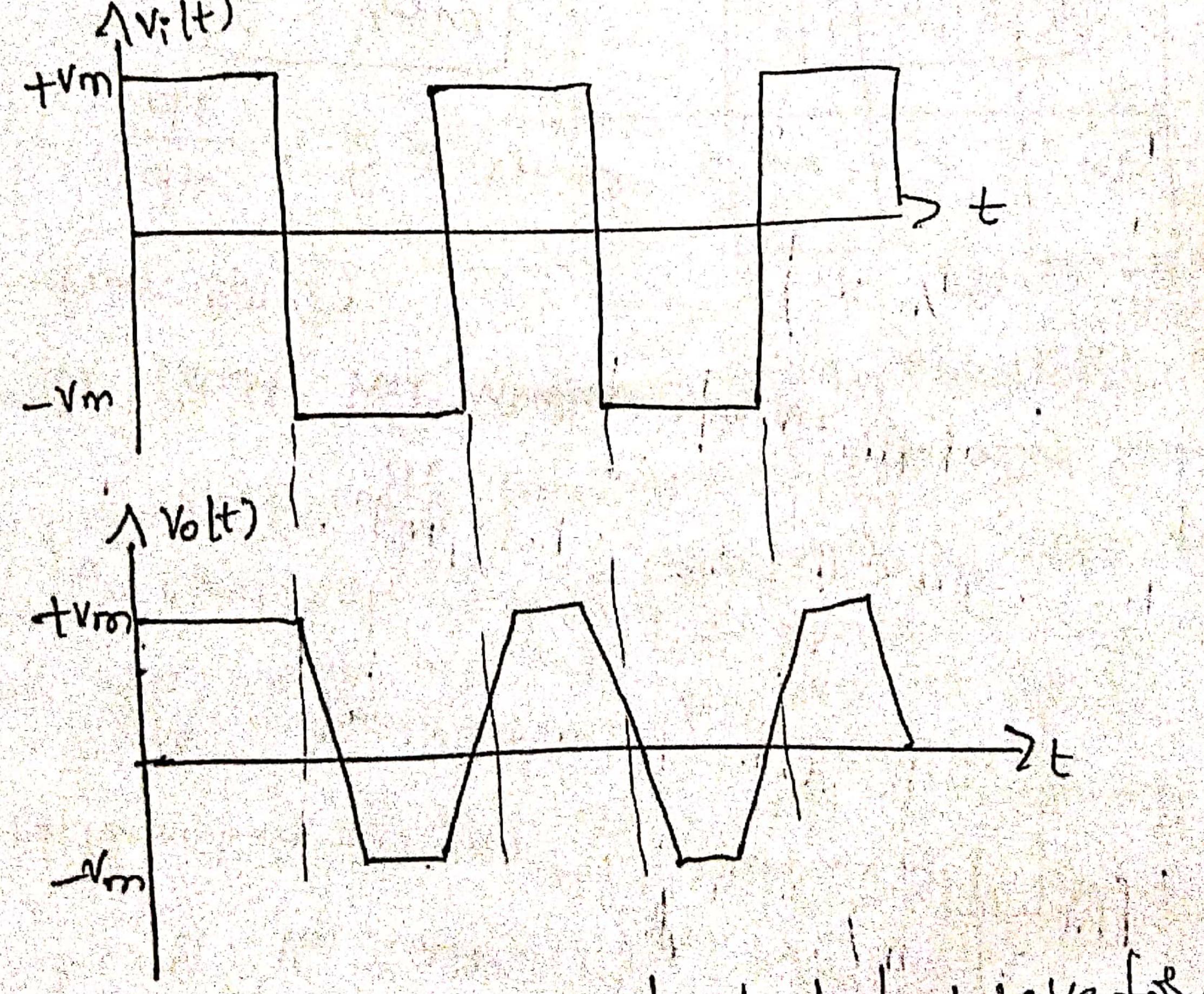

Consider a circuit using op. Amp having on? (16) Jain as shown below

-) If the ilp is Square wave then the olphas to be Square Dave but this is observed to Centain -frequency of ilp due to Slew Fate of an OP-Amp for a Particular ilp frequency olp gets distorted is shown below

7 Then observing such a distorted waveform on cho then slew hate can be obtained by

Skur Pale Ennhan.

Consider the unity Anin op. Amp Crt with Porty Sinuspidal sip the old must be some as ile

Vi Vin Cin wol

Vo: Vm Sinnel (2)

edifférentiale (5) wy l'1 !hun we get

dvo ... v. (0) Lol (u) (3)

The slow mate is defined as

C - dvo di- max

The Coswet bow manimum value is 1"

-from Ep (3)

= 2Ttfmw Vsec

1 this is the repuised claw sale Equation for distorted

7. The minimum allowable Irequency Im Gos be obtained of

1-1-m = -Sym 12)

-) Thú is also Called -full Power Bandwidth of the op Amp

the Vm is Peak of the olp wave form

I To operate the op-amp in non investing mode of operations the investing terminal should be grounded and the ilp sign

The old voltage is given by Vo= AOL-Vd = AOL (044) Vo = AOLVI -1 from the above Epritis clear that the olp signal is Exactly in Phase w.r.t the Elp Signal. 3. Differential mode operation: To operate the op-amp in differential mode Configuration 2 signal sources VI and V2 are applied to the non-inverting terminal and inverting terminal of op-Amp Respectively Vo= AOL. Vd The old voltage is given by Vo = AOL (VI -VL)

Closed loop operation.

OP-Amp Cannot operate linearly in open-loop mode but

the utility of an op-Amp Can be increases by operating it in

Closed loop mode. The closed loop operation is Possible with

the help of Lordhan

-) In the linear applications of op-amp is always used with -ve-feedback. The -ve-kedback helps in Controlling Jain which other

noise voltage at the sip terminal. The feedback is Provided by adding a sesistor Called - 1 a gesister Called Heedback resister as shown in fig: V2-00 Vo

-feedback resistor -> The feedback is Said to be regative as the feedback resistor Connects the olp to the investing ilp-terminal of the op-Amp. The Jain Resulting with feedback is Called closed bop Jain of the OP-AMP due to -feedback resistance is a reduction in the Bain. - The Closed loop gain is much less the open loop gain Advantages of -ve feedback. 1. It reduces the gain & makes it Controllable 2. It reduces the Possibility of distortion 3. It increases the Bandwidth ine frequency of operation. 4. It increases the Elp resistances of op-Amp 5. At decreases the olp resistances of op-Amp. 6. It reduces the Effects of temperature, Power Supply Jain of the Circuit Modes of operation in closed loop Configuration :-In closed loop Configuration there are 3 Possibilit modes of operation. They are 1. Enverting mode of operation 2. Non investing mode of operation 3 différential mode of operation

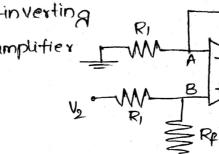

The Signal Source is Connected to the non-Investing terminal of optimp. and the -ve terminal is kept grounded through resistance Ri. To achieve the -ve feedback the feedback resistor Rt is Connected Hw vo and investing terminal of the op-Amp. Circuit Analysis:--Apply nodal Epo at node a. Circuit Fin VI = 0, the differential voltage of op-amp VI = 0 the voltage across node a is also Epuils to Dero Va=Vi \_\_\_(2) (2) in (1) Vi + Vi-Vo =0 V: (+++)=1 Vo = RITET Acl = 1+ Pt -) The gain of the non-investing OP. Amp is Either Unity Or greater than Unity is given by Proper adjustment of resistance (Rt and R1) 3: Differential operational Amplifier. VI -M

of the op-Amp through the gresistance R1 and Signal Source V1 is Connected to the non-investing teaminal of the op-amp through Vesistance R1 to achieve -ve teedback the feedback resistance R2 is Connected blow Vo and investing learning of op-Amp.

Circuit Analysis

Apply nodal Analysis at node a

i.e Vd = 0 for that Va=Vb

$$\frac{\sqrt[3]{2}}{\sqrt[3]{R_1}} + \frac{\sqrt{A_1}}{\sqrt[3]{R_1}} = 0$$

$$\sqrt{A_1} + \frac{\sqrt{A_1}}{\sqrt{A_1}} = 0$$

Sub @ in 4

$$\frac{V_0}{R_2} = \frac{V_1 - V_2}{R_1}$$

-1 The term of R2 is Called the Join of the operational

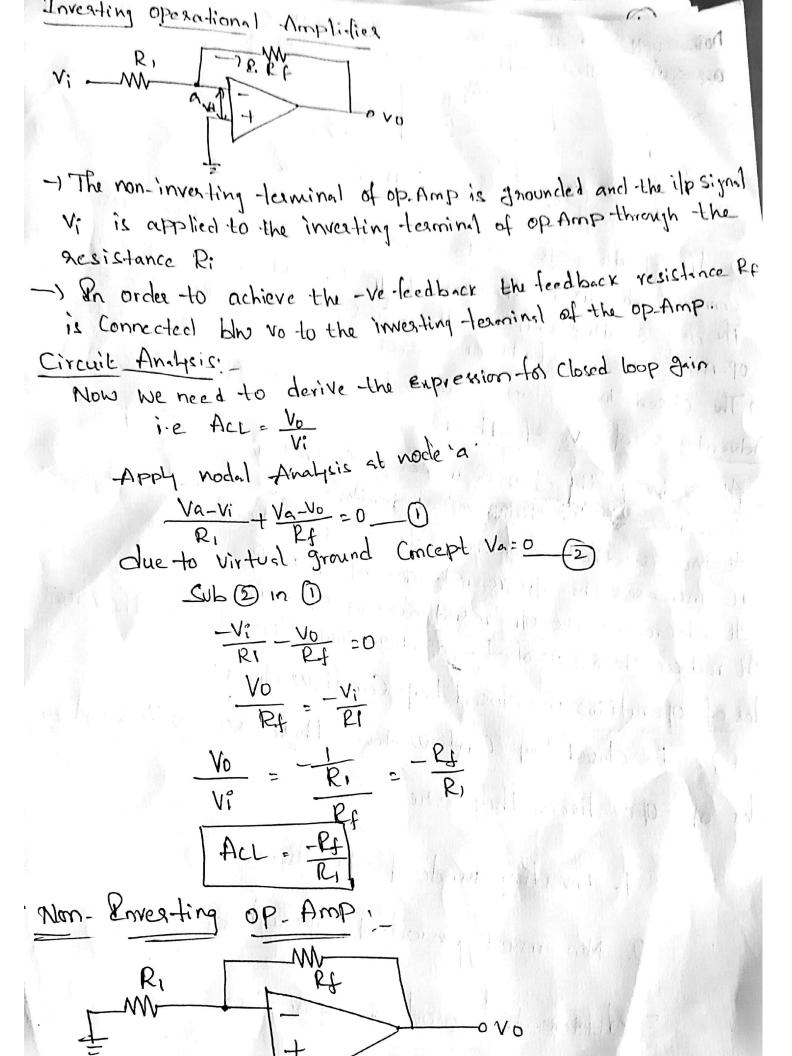

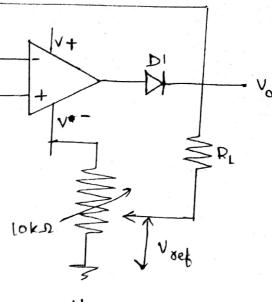

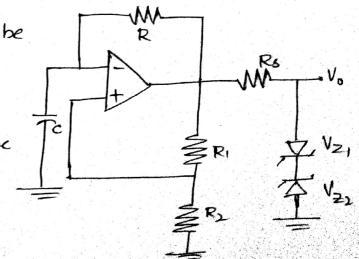

## 3) Negative clipper anthopositive reference vottage:

It clips the negative half aycle of input signal. The clipping level is determined by the reference voltage.

i) when  $V_i \in V_{ref}$ , the cliede  $D_i$  is on the open p walks as voltage follower and olp,  $V_0 = V_i$  (till  $V_i \in V_{ref}$ )

off, the op-amp operates in open loop

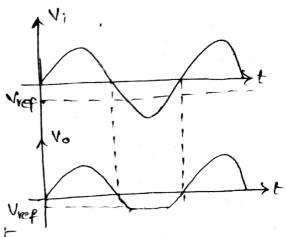

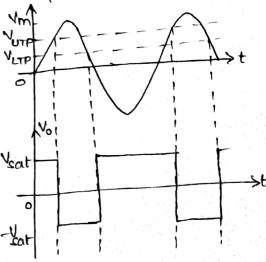

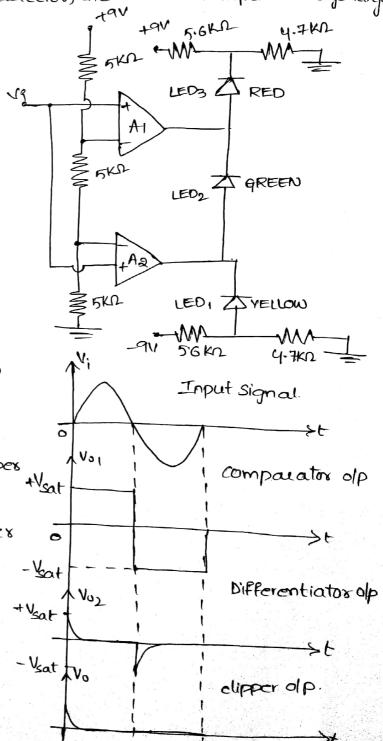

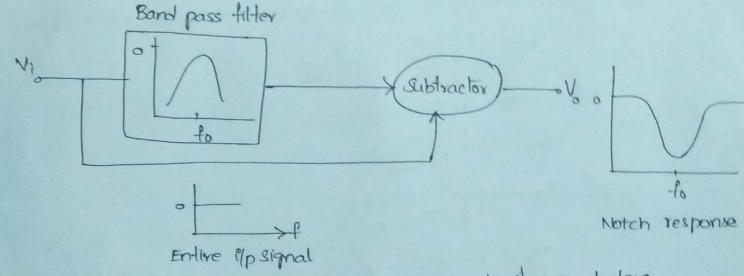

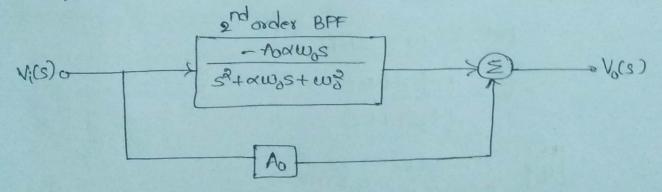

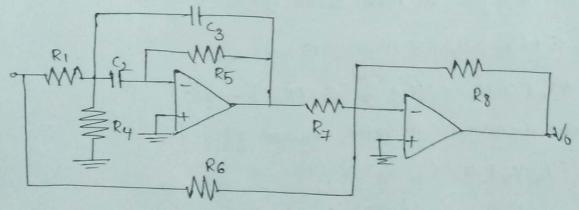

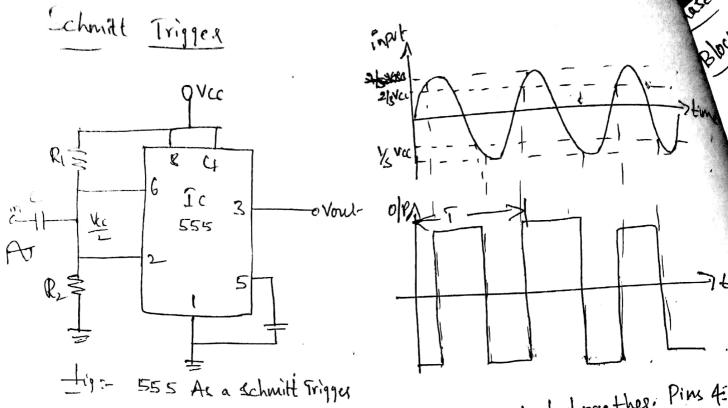

Regenerative Comparator (schmitt trigger);

If positive feedback is added to the comparator chuit, gain can be increased greatly.

The circuit is known as schmitt trigger. The input Voltage is feedback voltage at the (+) input terminal.

The input voltage vi triggers the output vo vipe every time it exceeds certain voltage levels.

These voltage levels are called upper Threshold Voltage three (Vin) and lower threshold voltage (Vit). The hysterisis width is the difference between these threshold voltages ie, voltages threshold voltages are calculated as follows.

$$\frac{V_{TP} - V_{ref}}{R_2} + \frac{V_{TP} - V_0}{R_1} = 0$$

$$V_{TP} \left[ \frac{1}{R_1} + \frac{1}{R_2} \right] = \frac{V_0}{R_1} + \frac{V_{ref}}{R_2}$$

$$V_{TP} = \frac{V_0 R_2 + V_{ref} R_1}{R_1 + R_2} + \frac{R_1 \cdot R_2}{R_1 + R_2}$$

$$V_{TP} = \frac{V_0 R_2}{R_1 + R_2} + \frac{V_{ref} R_1}{R_1 + R_2}$$

There are two types of triggering pants, Upper triggering point, VI > VOTP , Vo = - Vsat lower triggering point, VIZVLTP, Vo = + Vsat

upper triggering point.,

If

$$V_1 \subset V_{OTP}$$

,  $V_0 = + V_{SQL}$

$$V_{UTP} = \frac{R_1 V_{ref}}{R_1 + R_2} + \frac{V_{SQL} \cdot R_2}{R_1 + R_2} \quad V_{UTP}$$

$$V_{LTP}$$

for lower triggering point.

If

$$V_1 > V_{LTP}$$

,  $V_0 = -V_{SOA}t$

$$V_{LTP} = \frac{R_1 V_{ref}}{R_1 + R_2} - \frac{V_{SOA}t}{R_1 + R_2} = \frac{V_{SOA}t}{R_1 + R_2}$$

If  $V_1 < V_{LTP}$ ,  $V_0 = +V_{SOA}t$

The upper triggering voltage is always greater than lower triggering voltage i.e., VuTP > VLTP

(3)

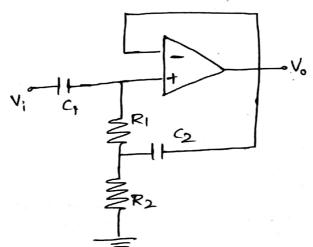

AC Amplifiers: Inverting and Non-Inverting amplifier responds to both ac and dc signals.

-> One wants to allow only ac signals and blocks of signal. This is provided by "Ac Amplifiers". This is achieved by using an Ac amplifier with a coupling capacitor.

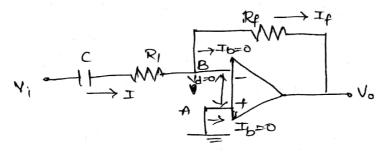

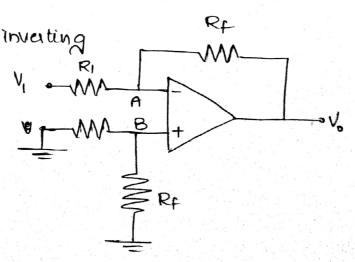

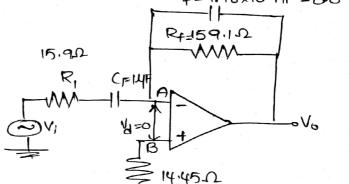

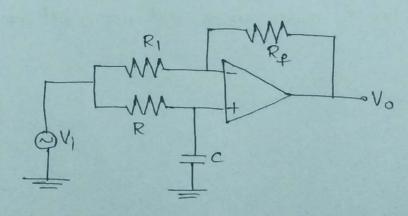

Inverting Ac Amplifier: - consider an ideal op-amp Ib=0; Vd=0

capacitor blocks de components and Ric toms 3dB frequency

Since

$$V_{d}=0$$

$V_{B}-V_{A}=0 \Longrightarrow V_{A}=V_{B}=0$

Apply KCL at node B., I=I1

$$\frac{V_1}{R_1 + \frac{1}{jwc}} = \frac{-V_0}{R_f}$$

$$\frac{V_0}{V_1} = \frac{-R_{\ell}}{R_{\ell} + \frac{1}{j \omega c}}$$

$$\frac{V_0}{V_i} = \frac{-R_f \cdot j\omega c}{R_i(\frac{1}{R_i} + j\omega c)}$$

To allow frequency 'c' value must be high.

$$\frac{V_0}{V_1} = \frac{-R_f}{R_1} \Rightarrow In this V_1 is only as signal.$$

In s-domain, s=jw

M

$$\frac{V_{0}(s)}{V_{1}(s)} = \frac{-Re}{R_{1} + \frac{1}{jsc}}$$

$$\frac{V_{0}(s)}{V_{i}(s)} = \frac{-R_{f}sc}{1+R_{i}sc}$$

$$= \frac{-R_{f}}{R_{i}} \left[ \frac{s}{\beta + \frac{1}{R_{i}c}} \right]$$

where  $w_{L} = \frac{1}{R_{i}c}$

$$Now_{i} \frac{V_{0}(s)}{V_{i}(s)} = \frac{-R_{f}}{R_{i}} \left( \frac{s}{s+w_{L}} \right)$$

$$S = jw$$

$$\frac{V_{0}}{V_{1}} = \frac{-R_{f}}{R_{i}} \left( \frac{jw_{i}w_{L}}{jw_{L}w_{L}} \right)$$

$$= \frac{-R_{f}}{R_{i}} \cdot \frac{1}{w_{L}} \left( \frac{j(w_{i}w_{L})}{j(w_{i}w_{L})+1} \right)$$

$$Now_{i} \cdot \frac{V_{0}}{V_{i}} = \frac{-R_{f}}{R_{i}} \left[ \frac{j(\frac{1}{f(f_{i})})}{1+j(\frac{1}{f(f_{i})})} \right]$$

At Respect to the second sec

At frequency  $f=f_L$ , the corresponding gain is given by  $\frac{V_0}{V_1} = \frac{R_F}{R_1} \left[ \frac{J}{I+1} \right]$

Now

$$\left| \frac{V_0}{V_f} \right| = \frac{R_f}{\sqrt{a}R_f}$$

Thus from above equation, we can conclude that the magnitude of gain is reduces to 3 dB from its highest value.

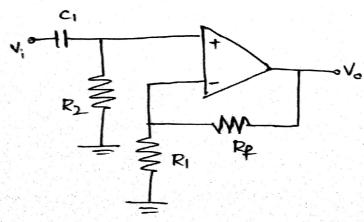

Non-Inverting A.C Amplifier:

-> Hence resistance R2 is added to provide [flow of dc component] to the ground towever, this reduces the overall itp impedance of the amplifies which now becomes approximately R2.

-> The problem of low ilp impedance is eliminated by connecting a capacitor is as shown in the below figure.

-> Capacitor & is large enough to act as short circuit to the

-> +ve terminal and node 'n' will be at the same potential, so signals. that Rz corriers almost no current. Hence, the circuit will have extremely high 11p impedance

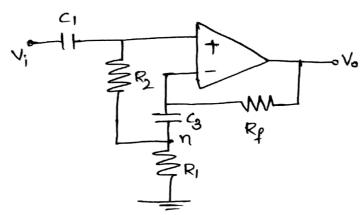

Ac voitage follower (Ac voitage Buffer):

-> This circuit used as a buffer to connect a high impedance signal source and a low impedance load which may be

-> the capacitor 4 and 62 are choosen high so that they are that circuited at all frequencies of operation.

3

-> The resistors R and R provide a path for ac input current into the non-inverting terminal.

-> The capacitor (2 acts as a boost strapping capacitor and connects the resistance R1 to the olp terminal for the operation -> Hence, the ilp terminal for the operation

approximately R1 (according to Miller's theorem)

.. The circuit is voltage follower AcL=1

ilp impedance =

$$\frac{R_1}{1-1}$$

= 00 == very high.

9

- 1) Voltage -follower

- 2) summing amplifier

- a) Investing summing amplifier

- 6 Non-Inverting summing amplifier

- c) subtractor

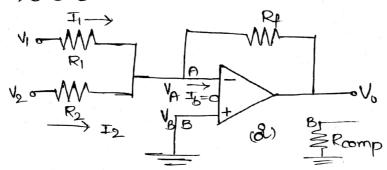

## 2) Summing amplifier;

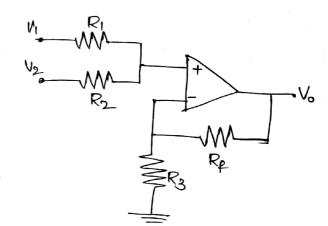

a) Inverting summing amplifier

VA=0 (By virtual ground concept)

Apply nodal analysis, kul at node A,

$$\frac{V_{A}-V_{0}}{R_{1}} + \frac{V_{A}-V_{1}}{R_{1}} + \frac{V_{A}-V_{2}}{R_{2}} = 0$$

$$\frac{-V_0}{R_f} - \frac{V_1}{R_1} - \frac{V_2}{R_2} = 0$$

$$V_0 = -R_f \left( \frac{U_1}{R_1} + \frac{V_2}{R_2} \right)$$

If  $R_1 = R_2 = R_f = R$  then it is adder.

if RI=R2=R and R\*Rf then it is an inverting amplifier.

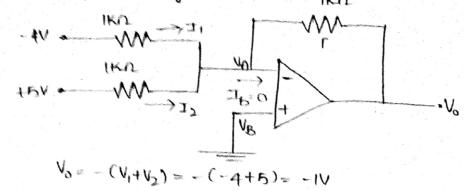

$$R_1 = R_2 = R_L = R \implies V_0 = -(V_1 + V_2) \implies Adder$$

$$R_1 = R_2 = R$$

and  $R_f \Rightarrow R$  then  $V_0 = -\frac{R_1(V_1 + V_2)}{R_1}$

Ly Inverting Amplifier.

Roblems

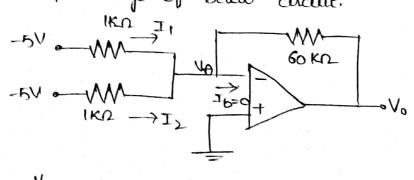

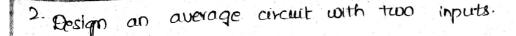

1. Find the output voltage of the below circuit.

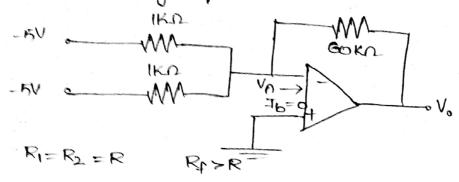

& Find the old voltage of the below circuit.

:.

$$V_0 = -\frac{R_F}{R_1}(V_1 + V_2) = -\frac{60K}{1K}(-5-5)$$

3. Find the olp voltage of below circuit.

$$\frac{-\frac{V_0}{60K} + \frac{5}{1K} + \frac{5}{10K} = 0}{-\frac{V_0 + 300 + 30}{60K} = 0}$$

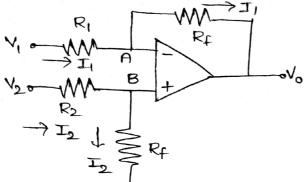

b) Non-Inverting summing amplifier

(8)

when the input signals are added & given to non-investing terminal of opening then it is called as Non-Investing.

$$V_{d} = V_{B} - V_{A}$$

$$V_{d} = 0 \implies V_{B} = V_{A} \longrightarrow 0$$

Addy voltage division rule,

$$V_A = \frac{V_0 \cdot R_1}{R_1 \cdot R_1} \longrightarrow (2)$$

Apply modal analysis at B., V3.

$$V_{B} = V_{A} \rightarrow 0$$

$V_{B} = V_{A} \rightarrow 0$

$V_{B} = V_{A} \rightarrow 0$

$V_{A} = V_{A} + V_{A}$

$$\frac{V_{B}-V_{1}}{R_{2}} + \frac{V_{B}-V_{2}}{R_{3}} + \frac{V_{B}-V_{3}}{R_{4}} = 0$$

$$\frac{V_{B}}{R_{2}} \left( \frac{1}{R_{2}} + \frac{1}{R_{3}} + \frac{1}{R_{2}} \right) = \frac{V_{1}}{R_{2}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}$$

$$\frac{V_{B}}{R_{2}} \left( \frac{V_{1}}{R_{2}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}} + \frac{V_{3}}{R_{4}} + \frac{V_{3}}{R_{4}} \right) = 0$$

$$\frac{V_{B}-V_{1}}{R_{2}} + \frac{V_{B}-V_{2}}{R_{3}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}$$

$$\frac{V_{B}}{R_{2}} + \frac{V_{1}}{R_{2}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}$$

$$\frac{V_{1}}{R_{2}} + \frac{V_{1}}{R_{3}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}$$

$$\frac{V_{1}}{R_{2}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}$$

$$\frac{V_{2}}{R_{3}} + \frac{V_{1}}{R_{3}} + \frac{V_{2}}{R_{4}}$$

$$\frac{V_{3}}{R_{4}} + \frac{V_{1}}{R_{3}} + \frac{V_{2}}{R_{4}}$$

$$\frac{V_{2}}{R_{3}} + \frac{V_{1}}{R_{4}} + \frac{V_{2}}{R_{3}}$$

$$\frac{V_{2}}{R_{3}} + \frac{V_{1}}{R_{4}}$$

$$\frac{V_{3}}{R_{4}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}$$

$$\frac{V_{3}}{R_{4}} + \frac{V_{4}}{R_{3}} + \frac{V_{1}}{R_{4}}$$

$$\frac{V_{1}}{R_{2}} + \frac{V_{2}}{R_{3}} + \frac{V_{1}}{R_{4}}$$

$$\frac{V_{2}}{R_{3}} + \frac{V_{1}}{R_{4}}$$

$$\frac{V_{2}}{R_{3}} + \frac{V_{1}}{R_{4}}$$

Equate (2) & (3) from (1).

$$V_0 = \frac{R_1}{R_1 + R_f} = \frac{\left(\frac{V_1}{R_2}\right) + \left(\frac{V_2}{R_3}\right) + \left(\frac{V_3}{R_4}\right)}{\frac{1}{R_2} + \frac{1}{R_3} + \frac{1}{R_4}}$$

$$V_{0} = \left( \frac{\frac{V_{1}}{R_{2}} + \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{4}}}{\frac{1}{R_{2}} + \frac{1}{R_{3}} + \frac{1}{R_{4}}} \right) \cdot \left( \frac{R_{1} + R_{1}}{R_{1}} \right)$$

Assume  $R_2 = R_3 = R_4 = R$

$$V_{0} = \left(1 + \frac{R_{f}}{R_{I}}\right) \left[ \frac{V_{1}/R_{I} + V_{2}/R_{I} + V_{3}/R_{I}}{V_{R} + V_{R} + V_{R}} \right]$$

$$V_0 = \left(1 + \frac{R_F}{R_I}\right) \left(\frac{V_1 + V_2 + V_3}{R} \times \frac{R}{3}\right)$$

$$V_0 = \left(1 + \frac{R_f}{R_1}\right) \left(\frac{V_1 + V_2 + V_3}{3}\right)$$

Assume

$$1+\frac{R_f}{R_1}=3 \implies R_f=2R_1$$

$$V_0=(V_1+V_2+V_3)$$

This equation indicates non-inverting summing amplifier costs difference amplifier -

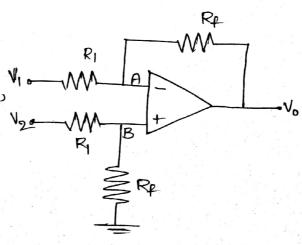

similar to the summer circuit, the subtraction of two input voltages is possible with the help of op-amp circuit, called subtractor. We difference amplifies circuit.

-> The circuit diagram is shown below.

The circuit analysis can be ovo done in two ways.

1) deper position Theorem.

Inorder to find the relation between the inputs & autputs, use superposition principle.

According to this, from the circuit the output voltage is given as  $V_0 = V_{01} + V_{02}$ , where  $V_{01}$  is the output voltage of the circuit when  $V_1$  is present and  $V_2$  is grounded (0).

$V_{02}$  represent the output voltage of the circuit when  $v_2$  is present and  $V_1$  is grounded (0).

case (i) 1-  $V_1$  is present and  $V_2 = 0$

The circuit books like inverting amplifier, for inverting  $V_1 = W_1$  amplifier, the output voltage is  $V_0 = -\frac{R_f}{R_1} V_9$ .

1

The circuit looks like non-inverting the autput voltage is

Apply voltage division rule.,

$$V_{02} = \left(\frac{R_1 + R_f}{R_1}\right) \left(\frac{V_2 \cdot R_f}{R_1 + R_f}\right)$$

$$V_{0} = \frac{V_{2} \cdot R_{f}}{R} \rightarrow 2$$

Total output voltage, Vo=Vo+Vo2

$$V_0 = -\frac{R_f}{R_1} \cdot V_1 + \frac{V_2 \cdot R_f}{R_1}$$

$$V_0 = \frac{+R_F}{R_I} \left( V_2 - V_I \right)$$

$$R_f > R_1$$

.,  $V_0 = \frac{R_f}{R_1} (V_2 - V_1) \Rightarrow$  Difference amplifier.

2) Wodal Analysis

Apply modal analysis at node A, 1,0 - M

$$\frac{V_{P}-V_{I}}{R_{I}}+\frac{V_{P}-V_{o}}{R_{f}}=0$$

$$V_A\left(\frac{1}{R_1} + \frac{1}{R_f}\right) = \frac{V_1}{R_1} + \frac{V_0}{R_0}$$

$$A = \frac{1 \times 1}{1 \times 1} \frac{1 \times 1}{1 \times 1} \frac{1 \times 1}{1 \times 1} \frac{1 \times 1}{1 \times 1}$$

$$V_A = \frac{V_1 R_1 + V_0 R_1}{R_1 + R_0} \rightarrow 0$$

Apply nodal analysis at node B,

Apply modal analysis at mode B.,

$$\frac{V_B - V_2}{R_1} + \frac{V_B - V_0}{R_F} = 0$$

$$\frac{V_B}{V_B} \left(\frac{1}{R_1} + \frac{1}{R_1}\right) = \frac{V_2}{R_1} + \frac{V_0}{R_F}$$

$$\frac{V_B}{V_B} = \frac{V_2 R_f + R_1 V_0}{R_1 R_F} \cdot \frac{R_1 \cdot R_F}{R_1 + R_F}$$

$$\frac{V_B}{R_1 \cdot R_F} = \frac{V_2 \cdot R_f}{R_1 + R_F}$$

$$\frac{V_B}{R_1 + R_F} = \frac{V_2 \cdot R_F}{R_1 + R_F}$$

$$\frac{V_1 R_f - V_2 R_f}{R_1 - V_2 R_1} = \frac{V_2 \cdot R_F}{R_1 + R_F}$$

$$\frac{V_1 R_f - V_2 R_f}{R_1} = -V_0 R_1$$

$$\frac{R_f}{R_1} = \frac{V_0}{V_2 - V_1}$$

$$\frac{V_0 = \frac{R_f}{R_1} (v_2 - V_1)}{V_2 - V_1}$$

problems 1-

1. Find the difference voltage for the following circuit

Sol:-

Il resistor values are equal.

$$V_0 = V_2 - V_1$$

$V_0 = -5 - (-5)$

$V_0 = 0V$

Rf

consider hyerting amplifier - VI o WM

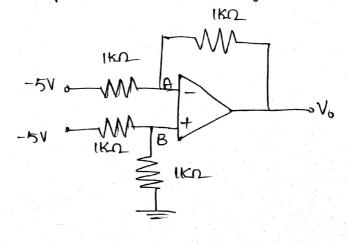

$$V_0 = -R_f \left( \frac{-V_1}{R_1} - \frac{V_2}{R_2} \right)$$

$$V_0 = R_f \left( \frac{V_1}{R_1} + \frac{V_2}{R_2} \right)$$

Assume

$$R_f = 10$$

$$R_1 = 1\Omega$$

|  $R_1 = 1 \times \Omega$

$R_1 = R_2 = 2\Omega$  |  $R_1 = R_2 = 2 \times \Omega$

RI

casecli):- consider non-inverting amplifier

$$V_{8} = (1 + \frac{R_{f}}{R_{3}}) \left( \frac{(V_{1}/R_{1}) + (V_{2}/R_{2})}{V_{1} + V_{1}} \right)$$

$V_{2} = (1 + \frac{R_{f}}{R_{3}}) \left( \frac{(V_{1}/R_{1}) + (V_{2}/R_{2})}{V_{1} + V_{2}} \right)$

$V_{2} = (1 + \frac{R_{f}}{R_{3}}) \left( \frac{(V_{1}/R_{1}) + (V_{2}/R_{2})}{V_{2} + V_{2}} \right)$

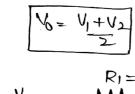

compare with  $V_0 = \frac{V_1 + V_2}{2}$

$$\left(\frac{1+\frac{R_1}{R_1}}{R_1}\right)=1$$

;  $R_1=R_2=1$  KD

$$\frac{R_4}{R_3} = 0 \implies R_4 = 0$$

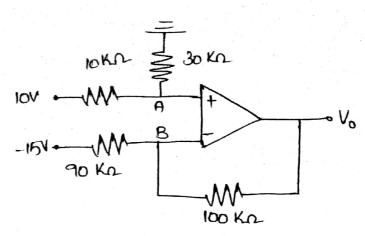

3 Find the output voltage of below circuit.

Apply nodal analysis

at node A.,

$$\frac{V_{A}-10}{306}+\frac{V_{A}-0}{306}=0$$

$$V_{A}\left(\frac{1}{10K} + \frac{1}{30K}\right) = \frac{10}{10K}$$

$$V_{A}\left(\frac{10}{4} + \frac{1}{40}\right) = 1$$

$$V_A = \frac{300}{40} \longrightarrow V_A = \frac{30}{4} V$$

(d) Apply voltage division whe,

$$V_{A} = \frac{10 \times 30 \text{ K}}{10 \text{ K} + 30 \text{ K}} = \frac{30}{4} \text{ V}$$

Apply nodal analysis at node B.,

$$\frac{V_{B}+15}{90K} + \frac{V_{B}-V_{0}}{100K} = 0$$

$$V_{B}(\frac{1}{90K} + \frac{1}{100K}) = \frac{-15}{90K} + \frac{V_{0}}{100K}$$

$$V_{B}\left(\frac{100+90}{90(100)}\right) = \frac{-15}{90} + \frac{V_{0}}{100}$$

$$\sqrt{B}\left(\frac{190}{90(100)}\right) = \frac{V_0}{100} - 0.166$$

$$V_B = \left(\frac{V_0}{100} - 0.166\right) \frac{1}{0.021}$$

$$\frac{30}{4} = 0.4733\% - 7.856$$

Differentiator: The civalit which produces the differentiation (1) of the input voltage at its output is called differentiator.

-> The differentiator circuit which doesnot use any active device called passive differentiator.

-> The differentiator circuit which using an active device like op-amp is called an active differentiator

Ideal op-amp Active differentiator-

The node B is grounded. The mode A is also at ground potential.

Apply KCL at node A-,

$$V_A = 0$$

$$c_1 \frac{d(-V_i)}{dt} = \frac{V_0}{R_p}$$

The product Reci is called time constant of the differentiator.

The negative sign indicates that there is a phase shift of 180° between input and output.

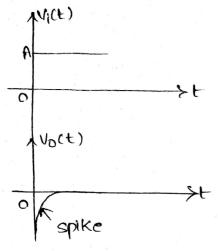

Input-autput waveforms of differentiator:

Assume Reci =1

Tistep the signal:

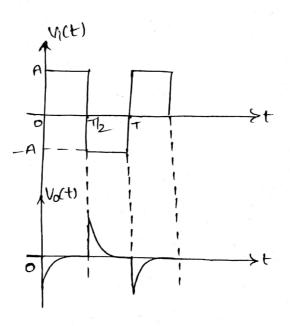

ii) Square input signal >-

$$V_i(t) = A O < t < T/2$$

$-A T/2 < t < T$

-> The differentiator behaves similar to its behaviour to stop input.

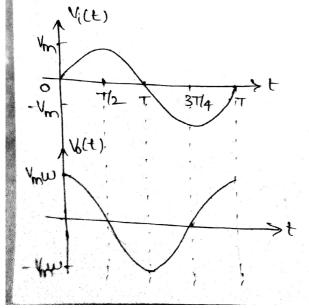

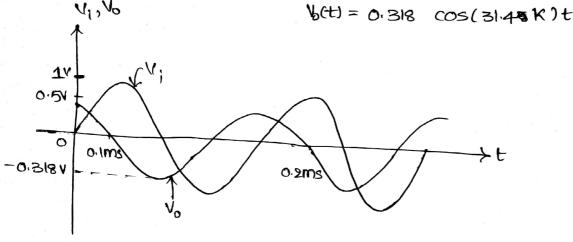

iii) Since wave input signal 1-

Vi(t)= A for t >0

Now

$$V(t) = -\frac{dV(t)}{dt} = -\frac{d(A)}{dt}$$

-> The step input takes a finite time to volts

-> Due to this finite time, the differentiated output is non-zero but appears in the farm of a spike at t=0

$$V_i(t) = V_m \sin \omega t$$

$V_0(t) = -\frac{d}{dt} V_i(t)$

$V_0 = -\frac{d}{dt} (v_m \sin \omega t) = -V_m \cos \omega t$

At  $t = 0$ ,  $V_0(t) = -V_m \omega$

$$t = T/4., V_0(t) = 0$$

$t = T/2., V_0(t) = V_m \omega$

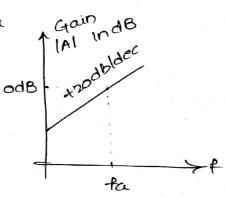

frequency response of Ideal differentiators

12

we know that the output voltage of ideal differentiator's given as  $V_0(t) = -R_F(i) \frac{dV_i(t)}{dt}$

Apply laplace transform.

Now, Gain of the differentiator is

$$\frac{V_0(s)}{V_i(s)} = -R_{\xi}(i(j\omega)) \quad (is=j\omega)$$

$$A = \frac{V_0(j\omega)}{V_1(j\omega)} = -j R_1 C_1 2\pi f$$

To obtain the frequency response, the magnitude of gain is

$$A = \left| \frac{V_0(j\omega)}{V_1(j\omega)} \right| = \left| -j\omega R_{f} c_1 \right| = \left| -j R_{f} c_1 \sum_{i=1}^{n} |f_i|^2$$

A = 2TH Reg

let, fa is the frequency at which gain becomes odB.

.. A can be written as, A = flfa

-> Gain in dB = 20 log A = 20 log (+/fa)

It feta., A indB is -Ve

Disadvantages 1-

- 1. Gain in dB increases at higher frequencies, which means the op-amp output goes to saturation means going to oscillate ic, system is unstable.

- a. At very high frequencies,  $x_c = 0$  It allows high frequency noise components and also amplifies it greatly.

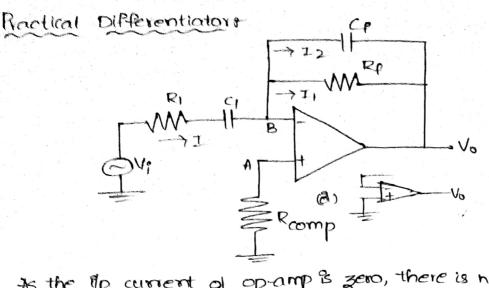

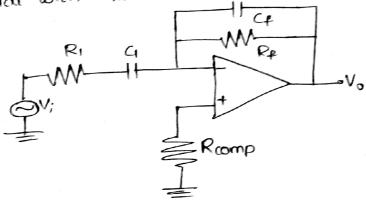

Is the fip current of op-amp's zero, there is no current at node A. Then  $V_A=0$

Circuit Analysis:

Apply KCL at mode B.,

$$\frac{V_i(s)}{R_l + \frac{1}{sc_1}} = \frac{-V_o(s)}{R_p} - \frac{V_o(s)}{V_s \ell_f}$$

$$V_{S}(S) \left( \frac{1}{R_{f}} + SC_{f} \right) = -\frac{V_{I}(S)}{1 + R_{I}SC_{I}}$$

Now,

$$\frac{V_0(s)}{V_i(s)} = \frac{-sqR_p}{(ftsR_{ci})(itsR_{fci})}$$

11 RICI = RICF

$$\frac{V_0(s)}{V_1(s)} = \frac{-s(_1R_f}{(_{1+sR_1(s)})^2} \rightarrow ()$$

Here Rea >> Ria (8) Rece but Rea <<T

Now eq. (1) becomes.,

No(s) = - SRf(1 V1(s) (: denominator is ignored)

$$V_0(t) = -R_{\xi}(1 \frac{d}{dt} v_i(t))$$

: It acts as a differentiator.

$$W-K.T., \frac{V_0(s)}{V_1(s)} = \frac{-sc_1R_f}{(1+sR_1C_1)^2} C R_1C_1 = R_f(c_f)$$

$$\frac{V_0(j\omega)}{V_1(j\omega)} = \frac{-j\omega C_1R_2}{(1+j\omega R_1(1)^2)} = \frac{-j\omega T_1R_2C_1}{(1+j\omega T_1C_1)^2}$$

let

$$f_b = \frac{1}{2\pi R_1 C_1}$$

;  $f_a = \frac{1}{2\pi R_2 C_1}$

Now,

$$\frac{V_0(j\omega)}{V_1(j\omega)} = \frac{-j(f_{+}\omega)}{(1+j(f_{+}\omega))^2}$$

Now, the magnitude is given as,

$$A = \left| \frac{V_0(j\omega)}{V_1(j\omega)} \right| = \left| \frac{-j(flea)}{(1+j(fleb))^2} \right|$$

Now, gain in dB = 20 log<sub>10</sub> A = 20 log<sub>10</sub>

$$\left(\frac{(f|f_a)}{(f|f_b)^2}\right)$$

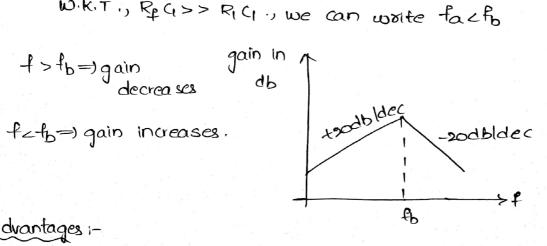

WKIT, REG>> RICI, we can write facto

Advantages :-

1. At high frequencies, gain is limited. So, circuit is stable.

2 Due to RiG and Rece combination, high frequency noise is just reduced.

Design of practical differentiates

1. Choose to as max trequency of input signal

3

$$f_b > f_a \Rightarrow |f_b = 10 f_a$$

problem: Design practical differentiator which differentiates the ilp sinusoidal with fmax = 200 Hz.

Soli- Given fa=200 Hz, let G=14F

$$\frac{1}{2\pi R_1 G} = 200 \implies R_f = \frac{1}{2\pi x} = 795.771$$

$$-1_{b} = \frac{1}{2\pi R_{1}G} \Rightarrow R = \frac{1}{2\pi x_{1} + x_{2} + x_{3}} = 49.57 \Omega$$

$$R_{f}(f = R_{i}G) = G = \frac{R_{i}G}{R_{f}} = \frac{79.57x_{i}M}{795.77}$$

2) Design the practical differentiator whose frequency is IKH2 (4) -fa= 1KH2 => fb=10(fa) 3×1:

$$R_1 = \frac{1}{2\pi x \, i0^6 x \, lox \, lo}^3$$

$$R_{comp} = R_{1} | R_{2}$$

$$= 2529.69$$

$$175$$

R1 = 15.92 G=9.78x108nF=009nF

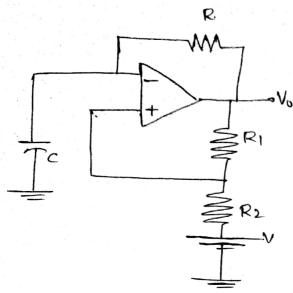

Integrator: The output voltage is the integral of input voltage is referred as integrator

1) passive integrator

= 14.45-2

The circuit using passive elements referred as passive Integrator.

2) Active Integrator

The circuit using active elements is referred as active Integrator.

Ideal Integrator (Active) Circuiti-

Apply kal at mode A,

$$I = I_1$$

$$\frac{V_1 - V_A}{R_1} = \frac{d}{dt}(V_A - V_0) C_f$$

$$\frac{V_1}{R_i} = -C_f \frac{d}{dt} V_0.$$

$$V_0 = \frac{-1}{R_1 C_4} \int_0^L V_0(t) dt \implies V_0 = \frac{-1}{R_1 C_4} \int_0^L V_0(t) dt$$

Refe is the time constant of the integrator

Rp(p>>7

Vox JV; dt means it acts as basic integrator circuit.

## Input & Output Wave-forms 1-

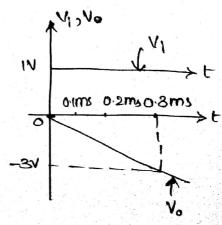

1) step input signal.

Assume Recp =1

Now,

$$v_0(t) = \int_0^t v_i(t) dt$$

=  $-A \int_0^t dt = -A(t)^t$

Thus, the old wave-form is a straight line with the slope of -A.

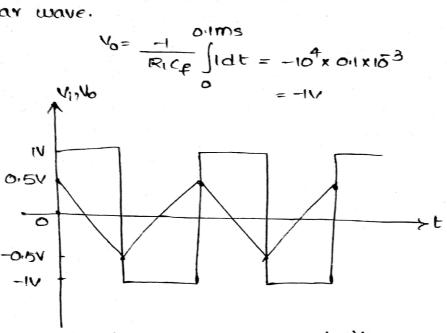

11) Equare wave input signal +

$$V(t) = \begin{cases} A & O < t < T/2 \\ -A & T/2 < t < T \end{cases}$$

Note,

$$V_{ACE} = -\int_{0}^{t} V_{i}(t) dt$$

$$= -\left[\int_{0}^{t} Adt + \int_{0}^{t} -Adt\right]$$

111) Sine wave input signal:

$V_1(t) = V_m \sin \omega t$   $No\omega$ ,  $V_0(t) = -\int V_p(t) dt$   $= -\int V_m \sin \omega t dt$   $V_0(t) = -\int V_m (-\cos \omega t)$   $V_0(t) = V_m \cos \omega t$

frequency Response of Heal Integrators

$$WKT.$$

,  $V_0 = \frac{-1}{R_1 c_4} \int V_i(t) dt$

Apply laplace transform, we get

$$\frac{V_0(S)}{V_1(S)} = \frac{-1}{SR_1C_{\mathbf{E}}}$$

Now, gain of integrated is

$$\frac{V_0(j\omega)}{V_1(j\omega)} = \frac{-1}{R_1(\epsilon_2)Tf}$$

Now gain,

$$A = \frac{-f_a}{P}$$

The magnitude of the gain is  $A = \left| \frac{f_a}{f} \right| = \frac{f_a}{f}$ Gain in dB=20 log (-falf)

At

$$f = 0$$

—) gain in  $dB = \infty$

$$f = f_a = gain in dB = odB$$

Disadvantages 1-

1. For ott3 = 1 gain is 00. It tip is not applied, due to ilp offset voltage, ilp bias ourrent, the olp is very high (error olp).

2. If ilp is applied, olp is not an exact integration of input due to vios and Ib.

3. Bandwidth is very less So, it is used as integrator to limited frequencies only.

-> To overcome this, we use practical integrator

practical Integrator +

The difference voltage, Vd=0

Apply nodal analysis at A.,

$$\implies -V_0\left(\frac{1}{R_1} + SC_{\frac{1}{2}}\right) = \frac{V_1}{R_1}$$

$$V_o(s) = \frac{-V_i(s)}{R_i(1+s\zeta_i R_p)}$$

$$V_0(s) = \frac{-V_p(s)}{\frac{R_1}{R_p}(1+Sc_pR_p)}$$

$$V_0(s) = \frac{-V_1(s)}{\frac{R_1}{1R_4} + sc_4R_1}$$

consider

$$R_1 >> R_1 >> 1 \implies \frac{R_1}{R_1} >> 1 \implies \frac{R_1}{R_1} << 1$$

$$V_0(S) = \frac{-V_1(S)}{1+SC_{\frac{1}{2}}R_1}$$

Apply inverse laplace transform.,

$$V_0(t) = \frac{-1}{R_1 C_1} \int V_1 dt$$

Input-output wave-18 ms of practical Integratori-

It is same as edeal integrator

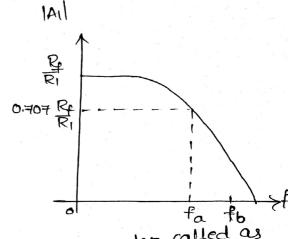

-figuency Response of practical integratori-

The output voltage of practical integrator in s-domain is given as

$$V_0(S) = \frac{-V_1(S)}{\frac{R_1}{R_2} + 1 + S C_1 R_1}$$

$$V_{\delta}(s) = \frac{-R_F V_1(s)}{R_1(1+SC_FR_F)}$$

$$A = \frac{V_0(S)}{V_1(S)} = \frac{-R_P}{R_1(1+j)2\Pi_P^2 R_P^2(C_P^2)}$$

fb> fa.,

$$A_1 = \frac{-R_1}{R_1(1+j(f(fa)))}$$

$$|A_1| = \frac{(R_f(R_1))}{\sqrt{1+(f_1f_0)^2}}$$

f≥fa., All > decreases

$$f=\infty$$

,  $|A_1|=0$

-> Fox pure integrator, gain is straight line. So, it is also called as "Lossy Integrator".

## Applications;

- 1. In analog computers.

- a. ADC'S

- 3. In wave shaping circuits.

- 4. To generate ramp signals.

steps to design practical integratori-1. select to as maximum input -frequency. 2. As fb>fa, choose fb is 10fa., fb=10fa ta = 16 3 Finding of Ry and Ri, fb=10 fa 2TI RICE 2TI RECE R4 = 10 R1 choose RIZIOKA 4. Consider  $t_b = \frac{1}{2\pi R_f C_f} \implies C_f = \frac{1}{2\pi R_f f_b}$ 5. Roomp = RI//Ry problems 1-1. Design lossy integrator with dc gain = 10 which integrates the Square input with frequency 10 KH2 <u>soli-</u> de gain =10 20 log (PalR1) = 10  $R_4 = R_1 10^2 = 3.16 R_1$ let R1=10KD., Rp = 81.6 KD From PRI // RA choose fa=10 KH2; fb= fa = 1KH2 2TIRECE = IK C-(=1 2T(R\_OK) = 5.03 n F

Rcomp = RILRY

9) Find the Values of R, and Rx. Given gain indis = todo

$$g$$

(1)

gain is decreased by 3dB at  $f=1.5$  kH $g$ ;  $C_1=0.14$  fr.

Sol:— At  $f=0$  H $g$ .,  $20 \log \left(\frac{R_1}{R_1}\right) = 40$

$$\frac{R_1}{R_1} = 100$$

$$3dB gain., 37 = 20 \log \left(\frac{100}{\sqrt{1+(1.5 K_1 R_1)^2}}\right)$$

$$10^{1.85} = \frac{100}{\sqrt{1+(1.5 K_1 R_1)^2}}$$

$$\frac{1}{10} = \frac{100}{\sqrt{1+(1.5 K_1 R_1)^2}}$$

3. Design a practical integrator whose frequency is  $10KH_2$ .

Sol:—  $f_0 = 10 KH_2$ :—

$$f_0 = \frac{1}{10} \implies f_0 = 1 KH_2$$

$$R_1 = 10 R_1$$

$$1et R_1 = 4K\Omega ., R_1 = 10 \times 9 K\Omega$$

$$R_2 = 90K\Omega$$

$$C_1 = \frac{1}{211} \frac{1}{R_1} \frac{1}{10} \implies C_2 = \frac{271 \times 100 \times 10^3 \times 10^3}{211 \times 100 \times 10^3}$$

$$C_3 = \frac{1}{211} \frac{1}{R_1} \frac{1}{10} \implies C_4 = \frac{1}{211} \frac{1}{R_1} \frac{1}{10}$$

$$= \frac{1}{211} \frac{1}{R_1} \frac{1}{10} \implies C_4 = \frac{1}{211} \frac{1}{R_1} \frac{1}{10}$$

$$= \frac{1}{211} \frac{1}{R_1} \frac{1}{10} \implies C_4 = \frac{1}{211} \frac{1}{R_1} \frac{1}{10}$$

$$= \frac{1}{211} \frac{1}{R_1} \frac{1}{10} \implies C_4 = \frac{1}{211} \frac{1}{R_1} \frac{1}{10}$$

$$= \frac{1}{211} \frac{1}{R_1} \frac{1}{10} \implies C_4 = \frac{1}{10} \frac{1}{10} \frac{1}{10} \implies C_4 = \frac{1}{10} \frac{1}{10} \frac{1}{10} \implies C_4 = \frac{1}{1$$

4. And the value of R, and Rp of integrator so that the peak gain is 20018 and the \$dB gain from its peak occur at w=10,000 rad/sec. capacitos of value or our . Given G = voluf +At 1=0=1 w=0 = dc gain = 20dB At w=10,000 rad/sec., 3dB gain = Max gain - 3dB = 20dB-3dB = 1798.  $\infty$  gain = 20 log  $\frac{Rf}{Ri}$ 20 = 20 log ( Rf/R1) 1 = log10 (R/R1)  $R_{t} = 10R_{1}$   $\longrightarrow$   $R_{t} = \frac{R_{t}}{10}$ 3dB gain = 20 wg (R/1+w2R2CP)  $17 = 20 \log \left[ \frac{R_f}{R_f} \frac{R_f}{1 + (104)^2 R_f^2 (0.014)^2} \right]$  $\frac{17}{20} = \log \left[ \frac{10}{\sqrt{1 + 10^8 R_0^2 \cdot 10^{-16}}} \right]$  $0.85 = \log \left( \frac{1}{\sqrt{1 + R_f^2 \cdot 10^{-8}}} \right)$ lug 10 - lug / 1+ R\$ 10 8 = 0,85  $\frac{1}{2}\log(1+10^{-8}R_{1}^{2})=\frac{3}{20}$ 1+10-8 R1= 100-3 108 Rf = 1.99-1 Rx 104 = 10.99

Rt = 9.94 KD => R = 0.9 KD

Soli- Apply nodal analysis at note A.,

$$\frac{V_{A}-V_{i}}{R.}+\frac{V_{A}-O}{V_{SC}}=0$$

$$V_A(\frac{1}{R} + SC) = \frac{V_i}{R} \implies V_A = \frac{V_i}{R} \cdot \frac{R}{1+SC}$$

At node B.)

$$\frac{V_B-0}{R} + \frac{V_B-V_0}{V_{SC}} = 0$$

$$V_{B}(\frac{1}{R} + SC) = \frac{V_{o}}{Y_{SC}}$$

$$V_0 = \frac{1}{SRC} V_1$$

Apply inverse laplace transform.,

6. Consider the integrator of type lossy whose component values are given as  $R_1 = 10 \, \text{KL}$ ,  $R_f = 100 \, \text{KL}$ ,  $C_f = 100 \, \text{F}$ . Determine the lower frequency limit of integration of study the response of input Signal. P) sine wave whose amplitude is 14 of frequency is 5 kHz.

11) step input

111) Square wave

Soli Given R= 10 KD, Rf=100 KD, Cf=107

$$f_a = \frac{1}{2\pi R_p C_p} \Rightarrow f_a = \frac{1}{2\pi \kappa_1 o^5 \kappa_1 o^9 \kappa_1 o}$$

i) sine wave, Amplitude = 14 frequency= 5 KHZ w=aTTf  $\omega = \mathfrak{M}(5K)$ w= 81.4 KH2 output of practical integrator,  $V_0(t) = \frac{-1}{R_1 c_R} \int V_1(t) dt$  $V_0(t) = \frac{-1}{(lok)(lon)} | sin (31.4k) t dt$ Vo(t) = cos (31.4K) t (31.4K) (0.1) 4,16 -0.318V

11) Step input, Ye = IV

consider oftensms

Vo at t=0.3 ms is

$$V_0 = \frac{1}{R_1 c_F} \int_{1.0}^{0.3 ms} \frac{0.3 ms}{0}$$

$$V_0 = \frac{-1}{(lok)(1000f)} \times (t)$$

No = -10 x0.3x103

$V_0 = -3V$ The output voltage is rampfunction., IV

(19)

IV peak Square wave

$$V_1 = \begin{cases} |V| & 0 \le t \le 0.1 \\ -iV & 0 : 1 \le t \le 0.2 \text{ ms} \end{cases}$$

The cultruit of each of these half periods will be ramps as seen above for step inputs, thus the expected of waveform will be triangular wave.

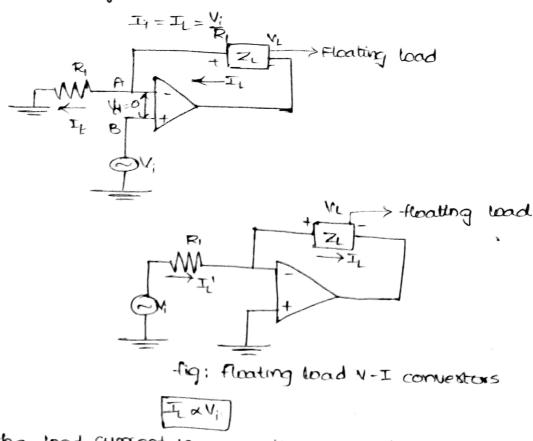

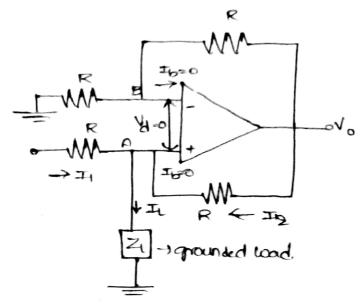

V-I convertor (voltage - current convertor):

In voltage to current convertor, the output load current is proportion to the input voltage

-> According to the connection of load, there are 2 types of V-I convertor

- 1. Voltage to current convestor with floating load.

- a Voltage to current convertor with grounded wad.

- -) It is also called as Transconductance amplifier.

1. Voltage to current convertor with floating loads

-> As input (voltage) current of op-amp is zero

-AThus, the load current is proportional to the input voltage and circuit walks on voltage to current converter.

8. Voltage to current converter with grounded load in

The shown in above figure, one end of the load impedance Zils arounded It is also known as "thowland aurent Converter".

VA = VB (: (VB-VA)=0)

Apply kal at mode A., I, + I2 = IL

ILR = V1+V0-2VA

F31 Investing amplifies, the  $V_0 = \frac{V_1 + V_0 - I_L R}{2} \rightarrow 0$  $= \left(1 + \frac{R}{R_1}\right) V_A$   $= \left(1 + \frac{R}{R}\right) V_A = 2 V_A$

Vo = 24 → 2

substitute the value of VA in eq. (1),

$$\frac{V_{R}}{R} = \frac{V_{1}}{2} = \frac{V_{1}}{2} + \frac{V_{2}}{R}$$

$$\frac{I_{L}R}{2} = \frac{V_{1}}{2}$$

$$I_{L} = \frac{V_{1}}{R}$$

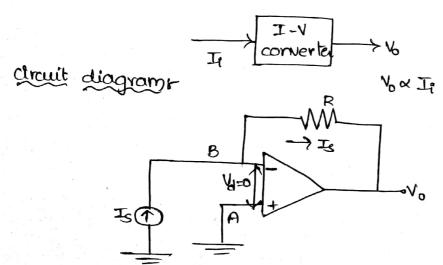

since R is constant, ILXV, Current(I) to Voltage (V) converter:

$\rightarrow$  In this, the olp voltage is proportional to its input awant.  $\rightarrow$  It accepts an Up (voltage) current Is and produces an output voltage, Vo such that  $V_0 = AI_8$ .

where A is the gain of the circuit.

(20)

-> since A is measured in ohms Because of this, I-V converters are also called transvesistance amplifier.

Circuit Analysist

$$V_{B}=0$$

$$V_{B}=V_{B}=0$$

$$V_{A}=V_{B} \qquad \text{Since } V_{A}=0 \implies V_{B}=0$$

$$V_{B}=V_{B} \qquad V_{B}=V_{B} \qquad V_{B}=0$$

$$V_{B}=V_{B} \qquad$$

The output voltage is proportional to the input current by the circuit walks as a current to voltage converter.

-> This circuit also referred as cultent controlled voltage source.

→ glf the resistance in the circuit is replaced by the impedance, I the circuit is called trans-impedance amplifier.

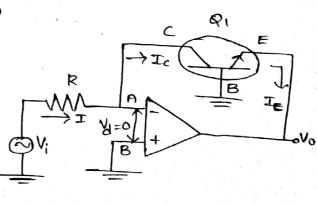

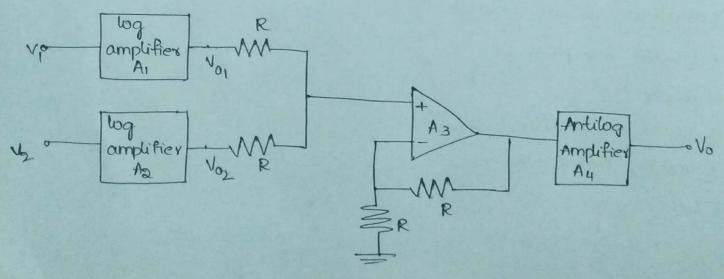

(Basic ) logarithmic Amplifier:

The voltage (output) of logasithmic amplifies is

Voa log (Vi)

(81) VoxIne(V1)

Basic lagarithmic circuit:

The difference Voltage, Vd=0

VA =O

Since transistor the base

terminal is grounded implies

I and I are equal.

The diode current equation

where  $I_s$  represents veverse saturation current and its value is  $10^{-13}A$ .

$$V_0 = \frac{-(1.38 \times 10^{-23} \times 300)}{1.60 \times \times 10^{19}} \ln_{e} \left( \frac{V_1}{10^{-13} \times 10^{3} \times 10^{3}} \right)$$

$$V_0 = -0.0258 \ln_{e} \left( \frac{V_1}{10^{-19}} \right)$$

cohen  $V_1 = 5mV$  then  $V_0 = -0.397V$  cohen  $V_1 = 50mV$  then  $V_0 = -0.45V$

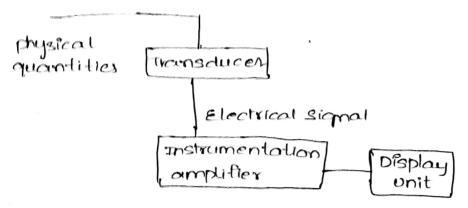

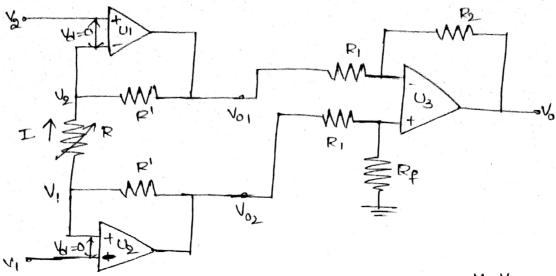

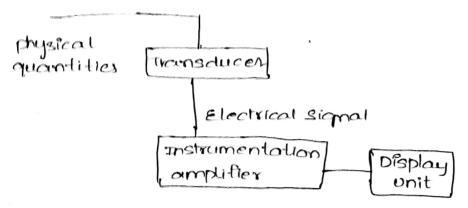

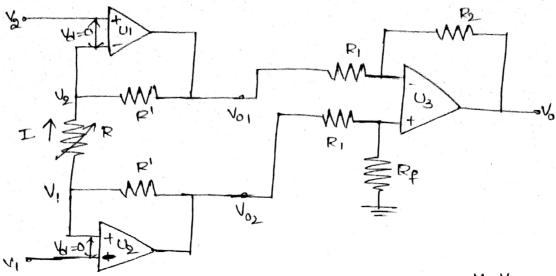

Instrumentation Amplifier =

The Instrumentation amplifies is mostly used in industrial applications in order to measure the change in physical quantities (Temperature, humidity, intensity...)

The basic chaut of instrumentation amplifies is a difference

Desive—the curlput voltage some

as difference amplifies output

Voltage.

At V1 terminal, the 1/p impedance

is R1.84 At V3 terminal, the 1/p

impedance is R1+R1.

Since the instrumentation amplifies is used in middle of past. It has to provide high input impedance and low output impedance with the use of difference amplifies it does not provide high input impedance. In order to provide high input impedance, a high impedance buffers are used before 4 and 4.

The current flows through the resistor R is  $I = \frac{V_1 - V_2}{R}$  If  $V_1$  and  $V_2$  are equal there is no current flow through the potentiometer R.

If

$$V_1$$

and  $V_2$  are not equal.,

$$-V_1 - IR' + V_{02} = 0$$

$$V_0 = V_1 + IR'$$

$$P' \longrightarrow -I$$

$$V_{02}$$

The old voltage of high impedance buffer (U1) is  $V_{01} = V_0 - IR'$

The olp voltage of difference amplifier is

$$V_{0} = \frac{R_{2}}{R_{1}} \left( V_{02} - V_{01} \right)$$

$$= \frac{R_{2}}{R_{1}} \left( V_{1} + IR^{1} - V_{2} + IR^{1} \right)$$

$$= \frac{R_{2}}{R_{1}} \left( (V_{1} - V_{2}) + 2 IR^{1} \right)$$

$$= \frac{R_{2}}{R_{1}} \left( \frac{2(V_{1} - V_{2})}{R} R^{1} + (V_{1} - V_{2}) \right)$$

$$V_{0} = (V_{1} - V_{2}) \left( \frac{R_{2}}{R_{1}} \left( 1 + \frac{2R^{1}}{R} \right) \right)$$

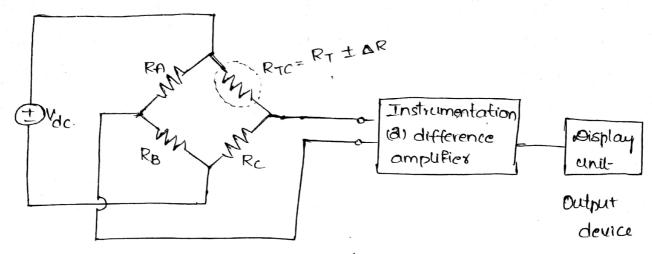

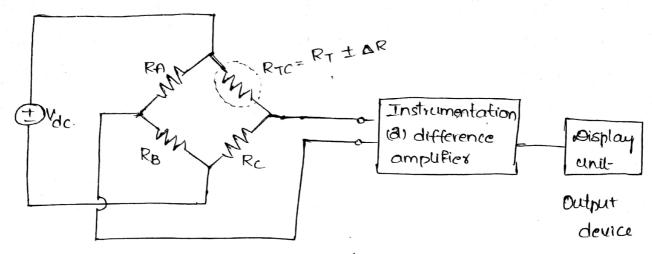

The instrumentation amplifier using transducer bridge (31) wein stone bridge.

Transduces / wein stone bridge

The transduces bridge uses a resistive element at one asm that depends on physical quantity. The Bridge is intially in balanced mode if there is a change in physical quantity then the bridge becomes unbalanced. This voltage is given as ilp to 3-op-amp instrumentational amplified which is used to drive the display worth.

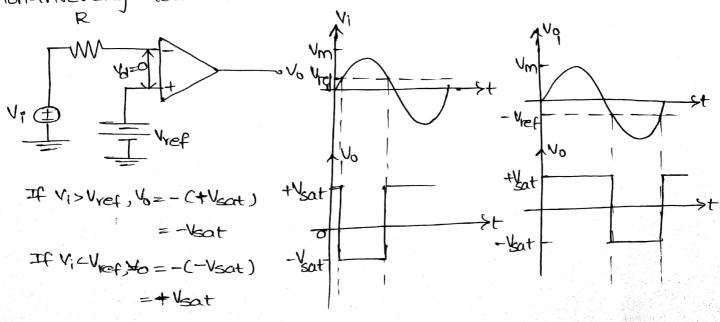

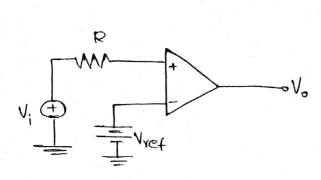

Comparators

The comparator using op-amp operates in open loop mode. For non-linear applications, the comparator is mainly used.

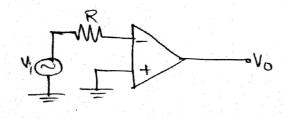

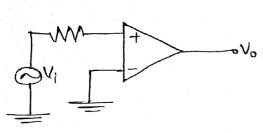

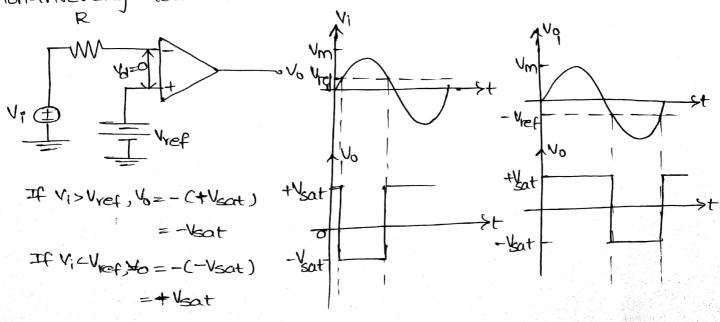

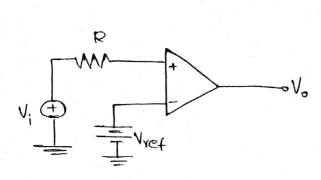

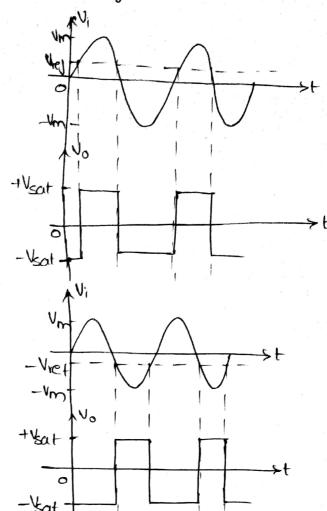

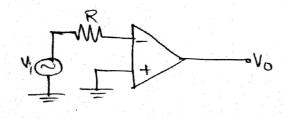

i) Inverting comparators when the input signal is given to inverting terminal of op-amp and a fixed of voltage is given to non-inverting terminal then it is called as Inverting comparator.

ii) Non-Inverting terminal, when the ilp signal is given to non-inverting terminal of op-omp e, the reference voltage is given to inverting terminal then it is called as Non-inverting comparator.

If Vi>Very, Vo=+(+Veat)

Vo=+Vsat

If Viz Vref, Vo = +(-Vsat)

=-Vsat

Applications of comparator -

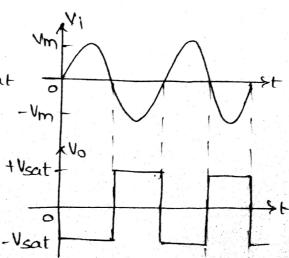

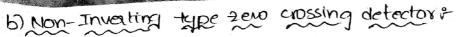

1. Zero Crossing defector, when the reference voltage is ov than the circuit is said to be in zero crossing defector mode.

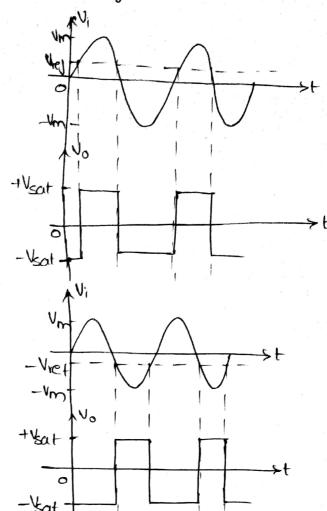

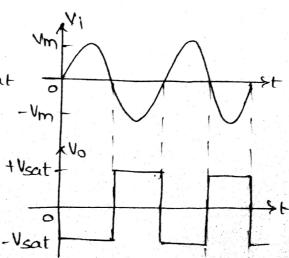

a) a Inverting type zero Crossing detector -

when  $V_1 > 0$ ,  $V_0 = -(+V_{Sat}) = -V_{Sat}$ when  $V_1 < 0$ ,  $V_0 = -(-V_{Sat}) = +V_{Sat}$

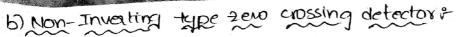

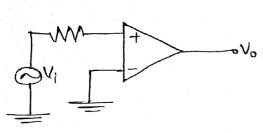

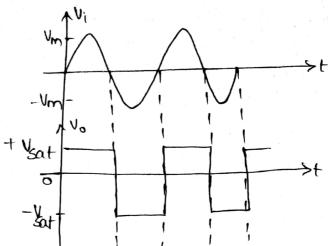

When  $V_i > 0$ ,  $V_0 = +(+V_{SQL}) = +V_{SQL}$ when  $V_i < 0$ ,  $V_0 = +(-V_{SQL}) = -V_{SQL}$

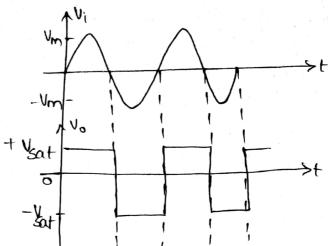

2) Window detector + By using the detector, the unknown input voltage range

can be found.

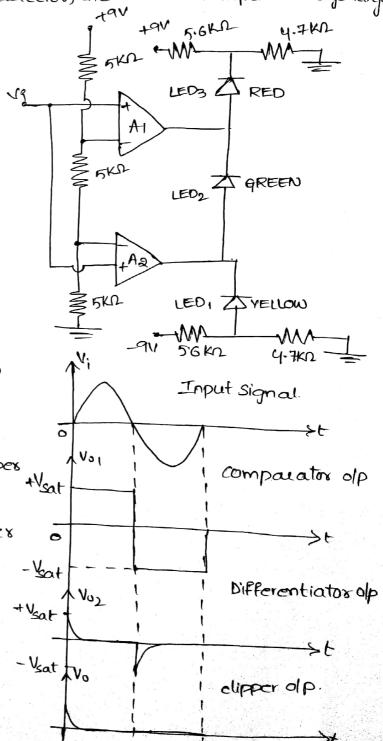

Ilp voltage Yellow Green Red

VICOV ON OFF OFF

ON OFF

VICOV OFF ON OFF

VICOV OFF OFF ON

3) Time masker generators

Non-inverting differenti biode clippes amplifies

It is used to generate trigger signals and mainly used in one shot (81) monostable multivibrator.

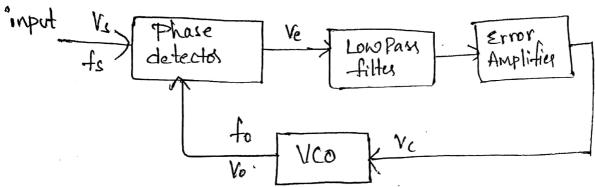

4 phase detector: It is some as time masker generator but at the input a phase detector is used

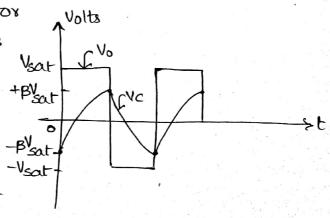

Multivibrators:

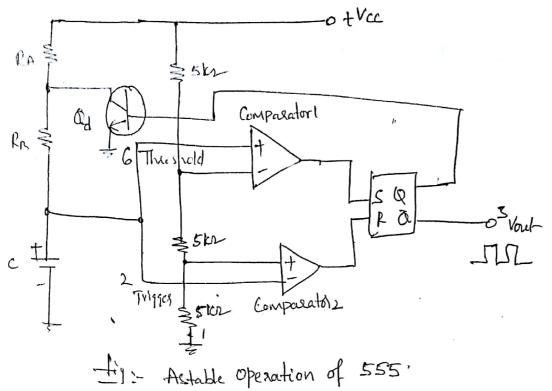

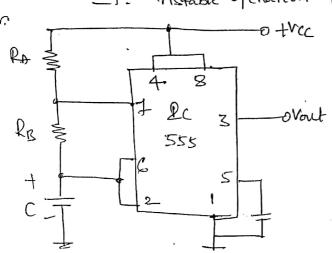

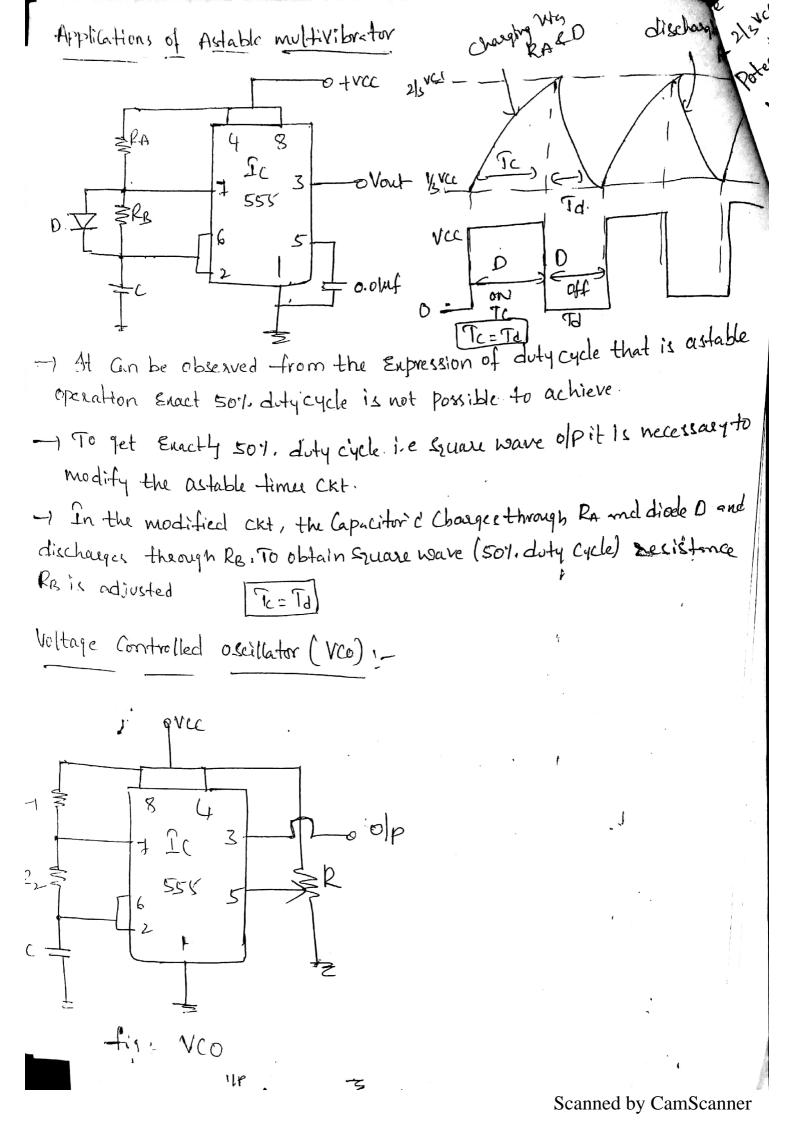

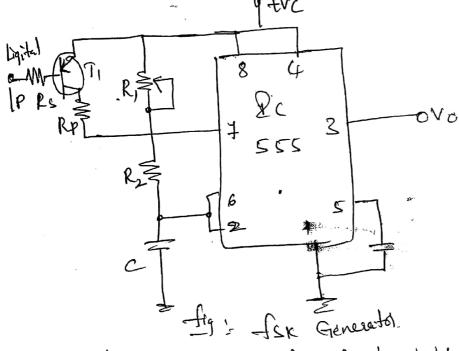

Astable Multivibrator -

It is also called as square wave generator on free running oscillator (81) Relaxation oscillator. In this 2 quasi stable states are present and it doesn't require any triggering to change its states.

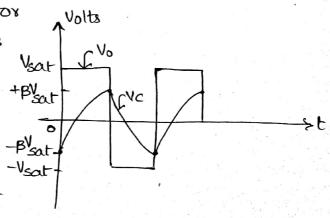

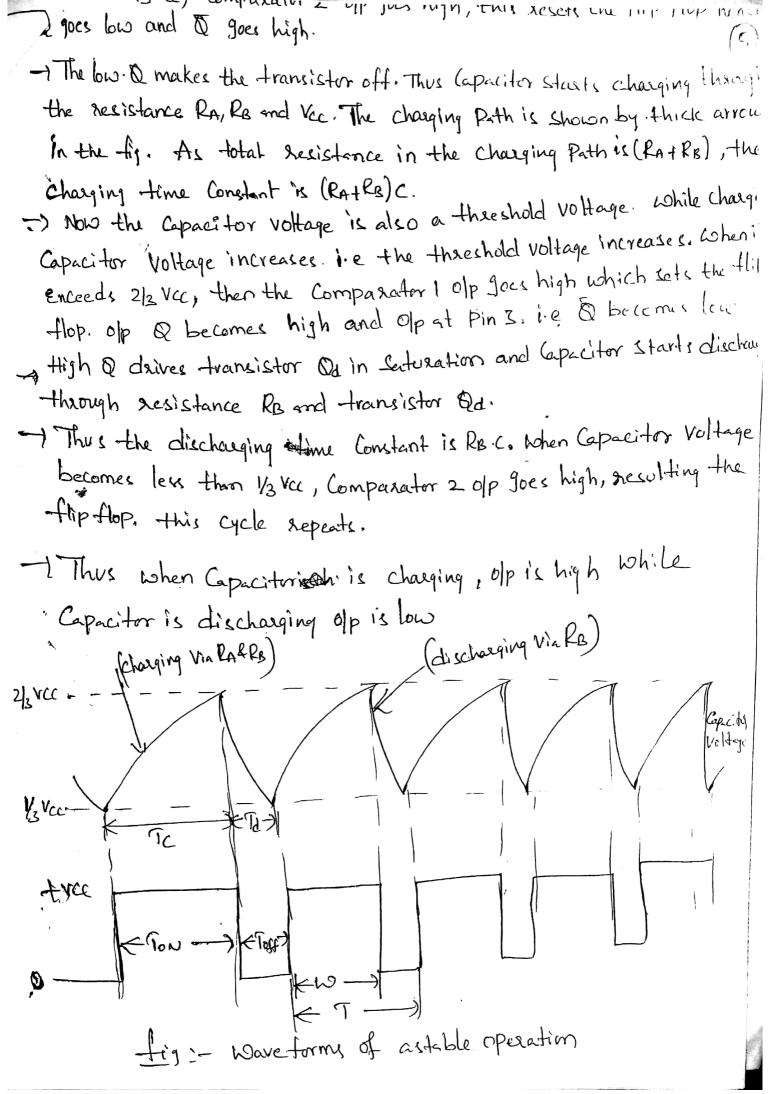

consider the output is at  $tV_{sat}$ . The voltage at the input terminal is  $tBV_{sat}$  (B is  $\frac{R_2}{R_1+R_2}$ ) at this instant of time, the aspacitor constants charging towards to  $tV_{sat}$

through the resistor Rowhen the voltage at inverting —

terminal becomes just greater than the reference voltage (+pVsat)

the output is suddenly drops to -Vsat. At this point, the capacitor starts discharging through resistor R of value -BVsat when the voltage at the inverting terminal becomes less than -BVsat. The output is driven to the Vsat & the cycle repeats.

frequency of Oscillations for Equare wave generator:

The voltage across the capacitor as a function of time is given as

from the waveforms,

$$V_f = +V_{\text{sat}}$$

$V_i = \beta V_{\text{sat}}$

$V_c(t) = V_{\text{sat}} + C - \beta V_{\text{sat}} - V_{\text{sat}} e^{-t/RC}$

$$(I+\beta) = TI | RC = I-\beta$$

$$= TI | RC = In \left(\frac{1-\beta}{1+\beta}\right)$$

$$T_{I} = RC | In \left(\frac{1+\beta}{1-\beta}\right)$$

$$T_{I} = T_{2}$$

$$\Rightarrow T = 2RC | In \left(\frac{1+\beta}{1-\beta}\right)$$

$$Assume | \beta = 0.5., | R_{I} = R_{2}$$

$$T = 2RC | In \left(\frac{3|_{2}}{1/2}\right)$$

$$T = 2RC | In \left(\frac{3|_{2}}{1/2}\right)$$

$$T = 2RC | In \left(\frac{3}{2}\right)$$

The peak to peak amplitude of square wave generated is  $V_{O(p-p)} = 2V_{sat}$

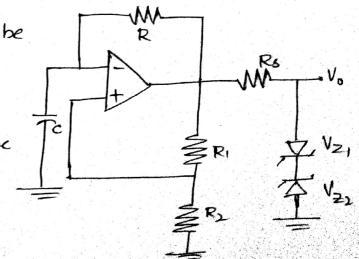

The amplitude can be varied, the power supply voltage. The peak amplitude can also be varied by making the power supply constant and the use of zener diodes connected back to back at the output. The output voltage is the summation of saturation voltage and zener break down voltage.

Symmetrical square wave can be generated if  $V_{21} = V_{22}$   $\Rightarrow T_1 = T_2$ Asymmetrical square wave can be generated if  $V_{21} \neq V_{22}$   $\Rightarrow T_1 \neq T_2$

An alternative method for generating asymmetrical square wave by using voltage to frequency converted

The capacitor charging and discharging voltages are given as:

changing voltage is +BVsat +V. discharging voltage is -BV satt

the ON time,

$$T_1 = RC \ln \left( \frac{1+B(Vos/Voi)}{Voi} \right)$$

The on time,

$$T_{1} = RC \ln \left( \frac{1+B(V_{02}/V_{01})}{1-B} \right)$$

The off time,  $T_{0} = RC \ln \left( \frac{1+B(V_{01}/V_{02})}{1-B} \right)$

problems:

1. Design a -free running oscillator with Ton of value orms and

Toff is 0.2 ms.

Given T = 0 lms

T=TON+TOFF

T=0.1+6.2 =0.3 ms

Assume B=0.5 (RI=R2)

let R= 10KD. => R=10KD

T=22RC =) (<1/4 =) C=0.1/4F

0.3x103 = 2.2 x Rx0.1x106

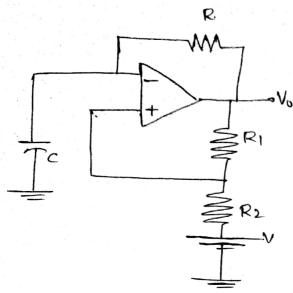

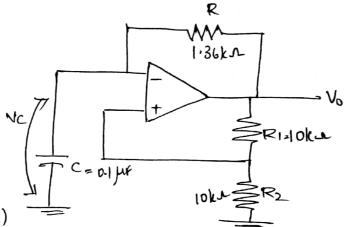

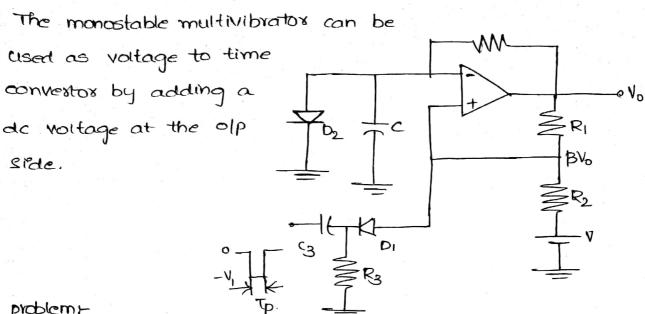

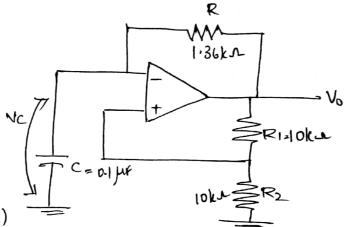

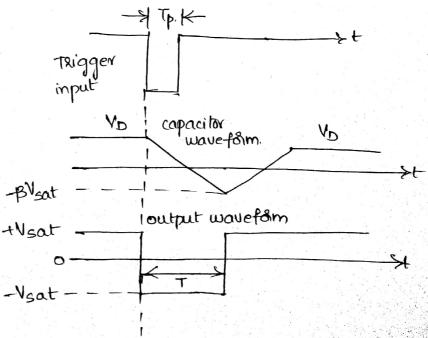

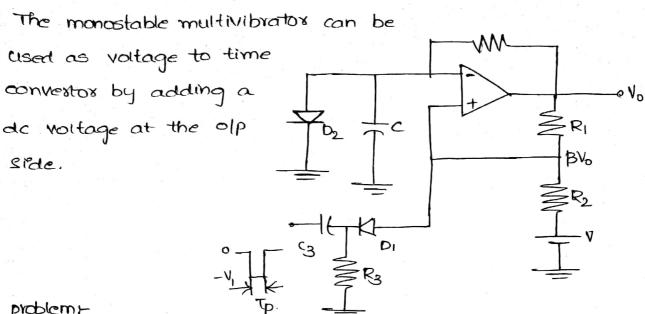

It is also called as one shot multivibrator delay circuit (a) gating circuit It needs one trigger pulse to change its state. The monostable multivibrator is used in sampling gates.

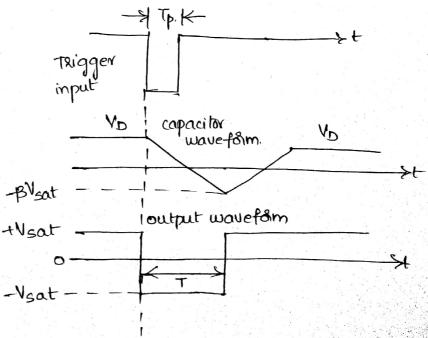

consider Vo is +Vsat. At this

Instant the capacitor starts

charging when the capacitor

voltage reaches to 0.7V.

The diode D2 will go ON

Implies Vc is clamped to

0.7V. A regative trigger

pulse is applied at the ATK

mon-inverting terminal of

op-amp whose voltage is BVsat-V, which is always 0.7V. Hance the cutput of op-amp will switch from +Vsat to -Vsat. Due to this the diade be will be in reverse bias E, the capacitor starts discharging to -Vsat through the resistor R. If the voltage at non-inverting terminal is high compared to investing terminal. The output of op-amp again switches from -Vsat to +Vsat and the cycle repeats.

the cycle repeats

Expression for pulse width:

The voltage across capacità is

$$V_c(t) = V_f + (V_i - V_f)e^{-t}$$

from the wavefam,  $V_f = -V_{Sat} + V_i = V_D$

$V_c(t) = -V_{Sat} + (V_D + V_{Sat})e^{-t}$  for the wavefam,  $V_f = -P_{Sat} + V_i = V_D$

$V_c(t) = -V_{Sat} + (V_D + V_{Sat})e^{-t}$  for  $V_{Sat} = -V_{Sat} + (V_D + V_{Sat})e^{-t}$  for  $V_{Sat} = -V_{Sat} + (V_D + V_{Sat})e^{-t}$  for  $V_{Sat} = V_{Sat} + (V_D + V_{Sa$

problem -

, Design a monostable multivibrator whose pulse width is 650 ysec, the Saturation Voltage is 9V, which is triggered by an input voltage & input pulse of value BV. Ethe time period 50 ysec.

Solit Given

$$-V_1=3V \Rightarrow V_1=-3V$$

$T_p=50 \text{ usec}$

$+V_{SA}t=\pm 9V$

$T=650 \text{ usec}$

$T=RC \text{ ln}\left(\frac{1}{1-\beta}\right)$

Assume  $\beta=0.5 \Rightarrow R_1=R_2=10 \text{ kn}$

$-T=0.693 \text{ Rc}$

$-50 \text{ use} = T$

$-10 \text{ let} = 0.693 \text{ let} = 0.495 \text{ let} = 0$

$$V_0 = \frac{-(1.38 \times 10^{-23} \times 300)}{1.60 \times 10^{19}} \ln_{e} \left( \frac{V_1}{10^{-13} \times 10^{3} \times 10^{3}} \right)$$

$$V_0 = -0.0258 \ln_{e} \left( \frac{V_1}{10^{-19}} \right)$$

cohen  $V_1 = 5mV$  then  $V_0 = -0.397V$  cohen  $V_1 = 50mV$  then  $V_0 = -0.45V$

Instrumentation Amplifier =

The Instrumentation amplifies is mostly used in industrial applications in order to measure the change in physical quantities (Temperature, humidity, intensity...)

The basic chaut of instrumentation amplifies is a difference

Desive—the curlput voltage some

as difference amplifies output

Voltage.

At V1 terminal, the 1/p impedance

is R1.84 At V3 terminal, the 1/p

impedance is R1+R1.

Since the instrumentation amplifies is used in middle of past. It has to provide high input impedance and low output impedance with the use of difference amplifies it does not provide high input impedance. In order to provide high input impedance, a high impedance buffers are used before 4 and 4.

The current flows through the resistor R is  $I = \frac{V_1 - V_2}{R}$  If  $V_1$  and  $V_2$  are equal there is no current flow through the potentiometer R.

If

$$V_1$$

and  $V_2$  are not equal.,

$$-V_1 - IR' + V_{02} = 0$$

$$V_0 = V_1 + IR'$$

$$P' \longrightarrow -I$$

$$V_{02}$$

The old voltage of high impedance buffer (U1) is  $V_{01} = V_0 - IR'$

The olp voltage of difference amplifier is

$$V_{0} = \frac{R_{2}}{R_{1}} \left( V_{02} - V_{01} \right)$$

$$= \frac{R_{2}}{R_{1}} \left( V_{1} + IR^{1} - V_{2} + IR^{1} \right)$$

$$= \frac{R_{2}}{R_{1}} \left( (V_{1} - V_{2}) + 2 IR^{1} \right)$$

$$= \frac{R_{2}}{R_{1}} \left( \frac{2(V_{1} - V_{2})}{R} R^{1} + (V_{1} - V_{2}) \right)$$

$$V_{0} = (V_{1} - V_{2}) \left( \frac{R_{2}}{R_{1}} \left( 1 + \frac{2R^{1}}{R} \right) \right)$$

The instrumentation amplifier using transducer bridge (31) wein stone bridge.

Transduces / wein stone bridge

The transduces bridge uses a resistive element at one asm that depends on physical quantity. The Bridge is intially in balanced mode if there is a change in physical quantity then the bridge becomes unbalanced. This voltage is given as ilp to 3-op-amp instrumentational amplified which is used to drive the display worth.

Comparators

The comparator using op-amp operates in open loop mode. For non-linear applications, the comparator is mainly used.

i) Inverting comparators when the input signal is given to inverting terminal of op-amp and a fixed of voltage is given to non-inverting terminal then it is called as Inverting comparator.

ii) Non-Inverting terminal, when the ilp signal is given to non-inverting terminal of op-omp e, the reference voltage is given to inverting terminal then it is called as Non-inverting comparator.

If Vi>Very, Vo=+(+Veat)

Vo=+Vsat

If Viz Vref, Vo = +(-Vsat)

=-Vsat

Applications of comparator -

1. Zero Crossing defector, when the reference voltage is ov than the circuit is said to be in zero crossing defector mode.

a) a Inverting type zero Crossing detector -

when  $V_1 > 0$ ,  $V_0 = -(+V_{Sat}) = -V_{Sat}$ when  $V_1 < 0$ ,  $V_0 = -(-V_{Sat}) = +V_{Sat}$

When  $V_i > 0$ ,  $V_0 = +(+V_{SQL}) = +V_{SQL}$ when  $V_i < 0$ ,  $V_0 = +(-V_{SQL}) = -V_{SQL}$

2) Window detector + By using the detector, the unknown input voltage range

can be found.

Ilp voltage Yellow Green Red

VICOV ON OFF OFF

ON OFF

VICOV OFF ON OFF

VICOV OFF OFF ON

3) Time masker generators

Non-inverting differenti biode clippes amplifies

It is used to generate trigger signals and mainly used in one shot (81) monostable multivibrator.

4 phase detector: It is some as time masker generator but at the input a phase detector is used

Multivibrators:

Astable Multivibrator -

It is also called as square wave generator on free running oscillator (81) Relaxation oscillator. In this 2 quasi stable states are present and it doesn't require any triggering to change its states.

consider the output is at  $tV_{sat}$ . The voltage at the input terminal is  $tBV_{sat}$  (B is  $\frac{R_2}{R_1+R_2}$ ) at this instant of time, the aspacitor constants charging towards to  $tV_{sat}$

through the resistor Rowhen the voltage at inverting —

terminal becomes just greater than the reference voltage (+pVsat)